## XMUT 101 Engineering Technology

A/Prof. Pawel Dmochowski

School of Engineering and Computer Science Victoria University of Wellington

CAPITAL CITY UNIVERSITY

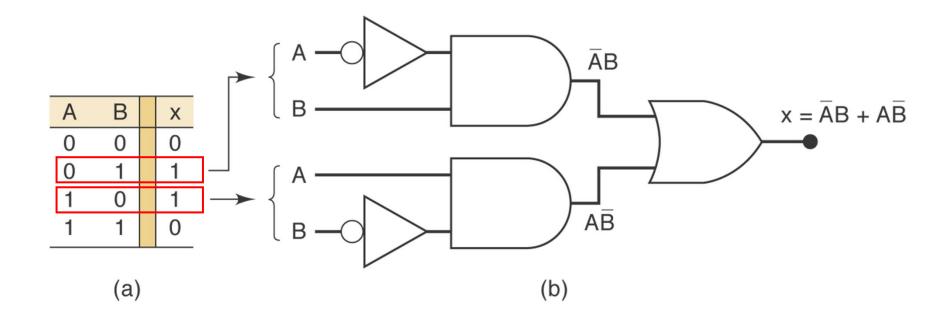

#### Exclusive OR and Exclusive NOR Circuits

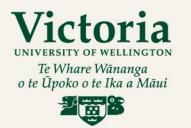

- The exclusive OR, abbreviated XOR produces a HIGH output whenever the two inputs are at opposite levels.

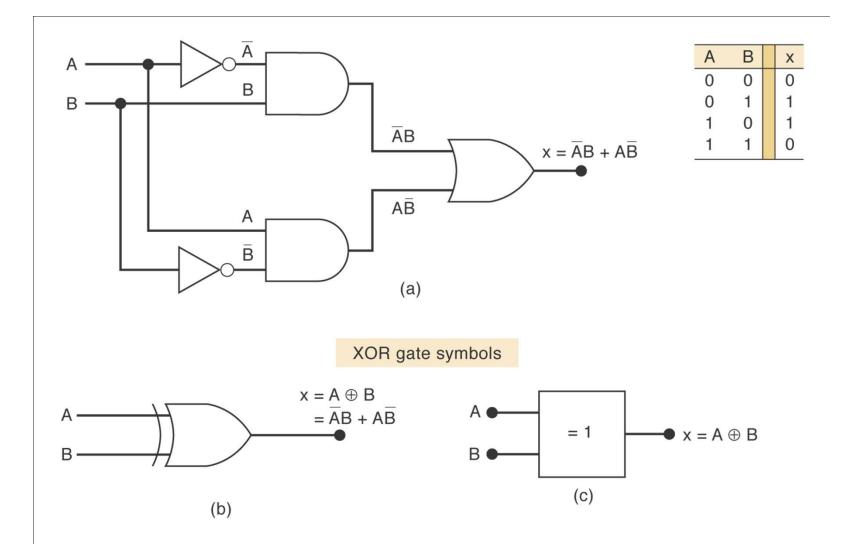

- The exclusive NOR, abbreviated XNOR produces a HIGH output whenever the two inputs are at the same level.

- XOR and XNOR outputs are opposite.

FIGURE 4-20 (a) Exclusive-OR circuit and truth table; (b) traditional XOR gate symbol; (c) IEEE/ANSI symbol for XOR gate.

FIGURE 4-21 (a) Exclusive-NOR circuit; (b) traditional symbol for XNOR gate; (c) IEEE/ANSI symbol.

4

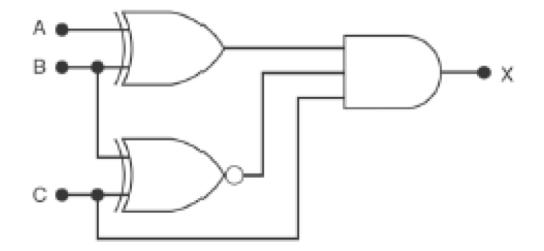

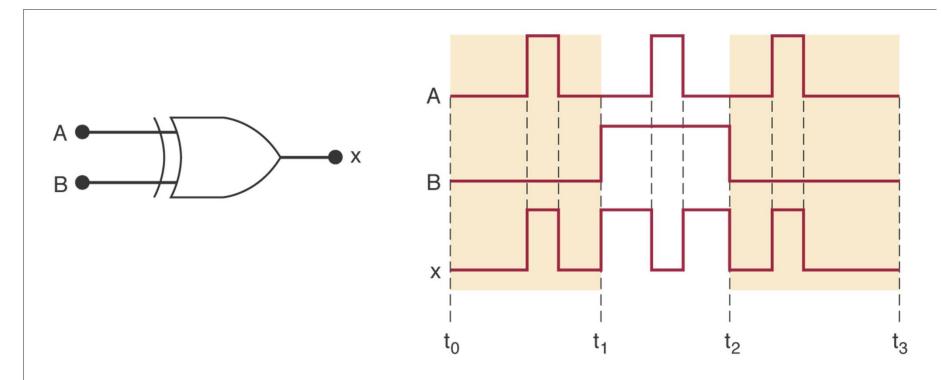

#### **Determine the O/P waveform of the circuit below:**

O/P Hi when I/P at different levels

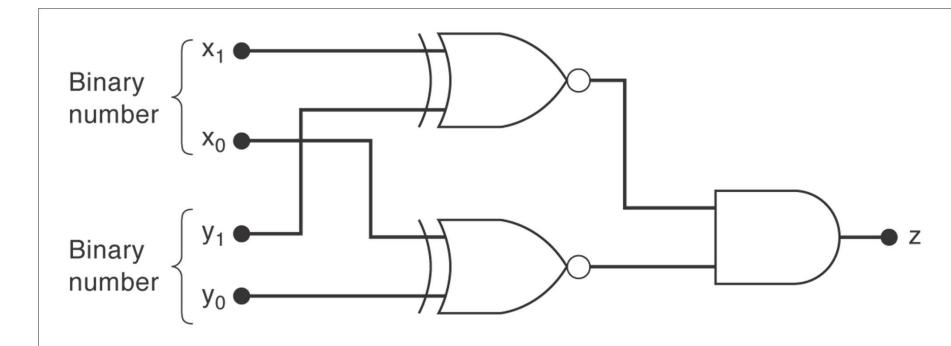

Design a circuit so that the O/P will only be HI when the combination of two sets of two bit binary numbers are equal.

| <b>X</b> 1 | <b>X</b> 0 | <u>У</u> 1 | <b>y</b> 0 | z (Output) |

|------------|------------|------------|------------|------------|

| 0          | 0          | 0          | 0          | 1          |

| 0          | 0          | 0          | 1          | 0          |

| 0          | 0          | 1          | 0          | 0          |

| 0          | 0          | 1          | 1          | 0          |

| 0          | 1          | 0          | 0          | 0          |

| 0          | 1          | 0          | 1          | 1          |

| 0          | 1          | 1          | 0          | 0          |

| 0          | 1          | 1          | 1          | 0          |

| 1          | 0          | 0          | 0          | 0          |

| 1          | 0          | 0          | 1          | 0          |

| 1          | 0          | 1          | 0          | 1          |

| 1          | 0          | 1          | 1          | 0          |

| 1          | 1          | 0          | 0          | 0          |

| 1          | 1          | 0          | 1          | 0          |

| 1          | 1          | 1          | 0          | 0          |

| 1          | 1          | 1          | 1          | 1          |

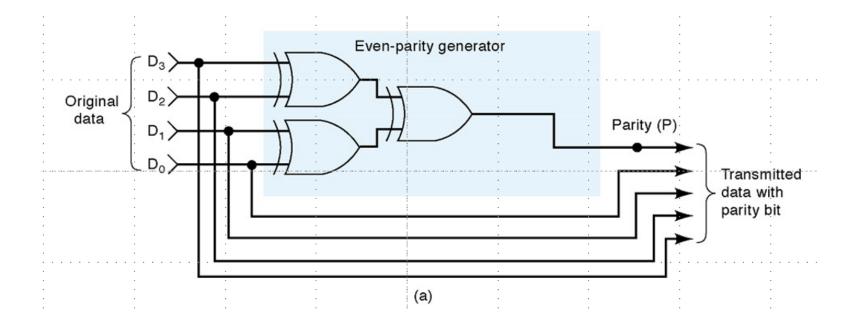

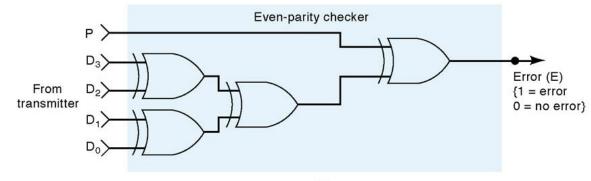

# Parity Generator and Checker

- Parity bit: extra bit added to data to make the number of 1's even (for even parity) or odd (for odd parity)

- It is used to detect error in transmission

- Example: if we use an even parity system:

- Data:  $1 \ 1 \ 1 \ 0$  we add a parity bit 1

- Data:  $1 \ 1 \ 0 \ 0$  we add parity bit 0

- Data:  $0 \ 0 \ 0 \ 0$  we add a parity bit 0

- A Parity Checker will return a TRUE error bit if the number of 1's is odd (for even parity) and if the number of 1's is even (for odd parity)

# Parity Generator

### $AB \oplus AB = \overline{AB} + A\overline{B}$ $\overline{AB \oplus AB} = \overline{AB} + AB$

- How to construct an even parity generator (3 bits input)?

- Truth table:

| Α | B | С | Ρ |

|---|---|---|---|

| 0 | 0 | 0 |   |

| 0 | 0 | 1 |   |

| 0 | 1 | 0 |   |

| 0 | 1 | 1 |   |

| 1 | 0 | 0 |   |

| 1 | 0 | 1 |   |

| 1 | 1 | 0 |   |

| 1 | 1 | 1 |   |

# Parity Generator $AB \oplus AB = \overline{AB} + A\overline{B}$ $\overline{AB \oplus AB} = \overline{AB} + AB$

- How to construct an even parity generator (3 bits input)?

- Truth table:

| A | B | С | Ρ |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

$$P = \overline{A}\overline{B}C + \overline{A}B\overline{C} + A\overline{B}\overline{C} + ABC$$

=  $\overline{A}(\overline{B}C + B\overline{C}) + A(\overline{B}\overline{C} + BC)$

=  $\overline{A}(BC \oplus BC) + A(\overline{B}C \oplus BC)$

=  $\overline{A}X + A\overline{X}$

=  $A \oplus B \oplus C$

## Parity Generator and Checker

#### Similarly for 4 bits (even parity):

## Parity Checker

- Exercise:

- Design an even parity **checker** (2 data bits) using a truth table

- Express it using XOR or XNOR gates

| Α | B | Ρ | Е |

|---|---|---|---|

| 0 | 0 | 0 |   |

| 0 | 0 | 1 |   |

| 0 | 1 | 0 |   |

| 0 | 1 | 1 |   |

| 1 | 0 | 0 |   |

| 1 | 0 | 1 |   |

| 1 | 1 | 0 |   |

| 1 | 1 | 1 |   |

## Parity Generator and Checker

### Similarly for 4 bits:

Even Parity:

## Karnaugh Map (K-Map)

- An alternate approach to representing Boolean functions

- Can be used to minimize Boolean functions

- Easy conversion from truth table to K-Map to minimized SOP representation.

- Simple rules (steps) used to perform minimization

- Leads to minimized SOP representation.

- Much faster and more efficient than previous minimization techniques with Boolean algebra.

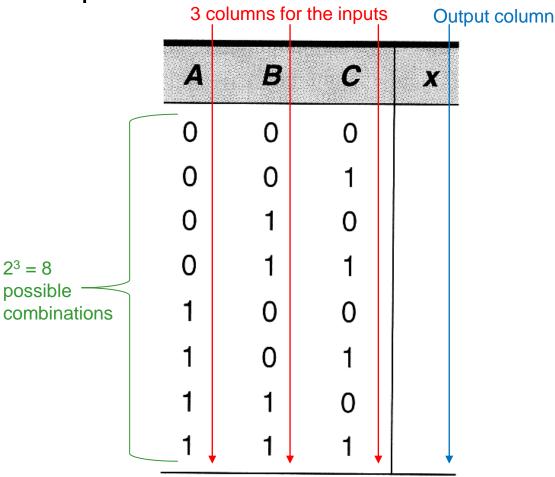

• The truth table values are placed in the K map as shown below.

| C<br>AB | C' | С |  |

|---------|----|---|--|

| A'B'    |    |   |  |

| A'B     |    |   |  |

| AB      |    |   |  |

| AB'     |    |   |  |

|         |    |   |  |

- The truth table values are placed in the K map.

- Adjacent K map square differ in only one variable both horizontally and vertically.

- The truth table values are placed in the K map.

- Adjacent K map square differ in only one variable both horizontally and vertically.

- The pattern from top to bottom and left to right must be in the form  $\overline{AB}, \overline{AB}, AB, AB$

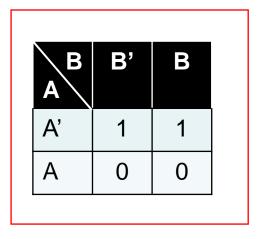

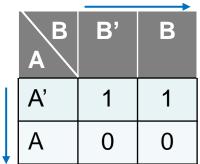

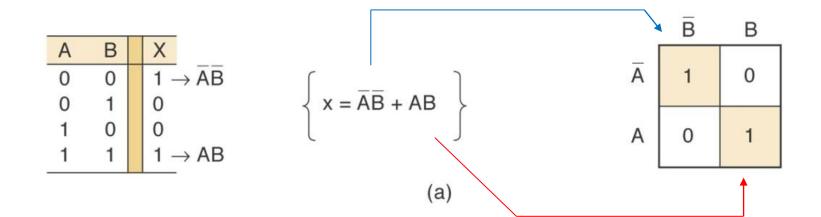

2 inputs:

- The truth table values are placed in the K map as shown in on next slide.

- Adjacent K map square differ in only one variable both horizontally and vertically.

- The pattern from top to bottom and left to right must be in the form  $\overline{AB}, \overline{AB}, AB, AB$

- A SOP expression can be obtained by OR-ing all squares that contain a 1.

- A Karnaugh map is a graphical tool for assisting in the general simplification procedure.

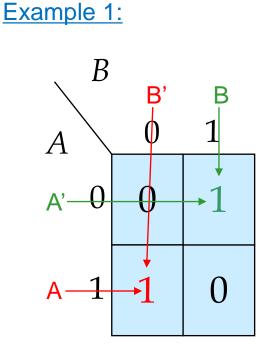

- Two variable maps.

F=AB'+A'B

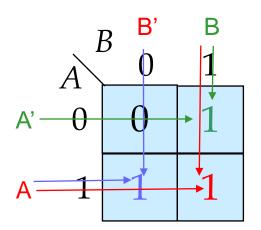

- A Karnaugh map is a graphical tool for assisting in the general simplification procedure.

- Two variable maps.

F = AB + A'B + AB'

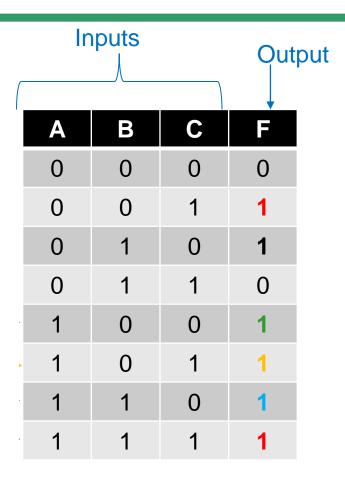

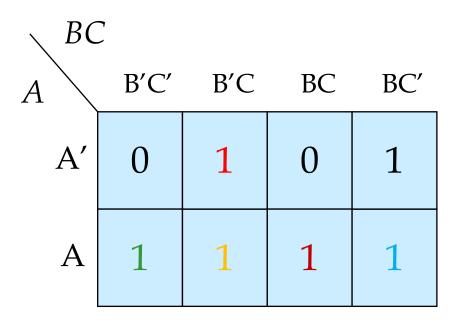

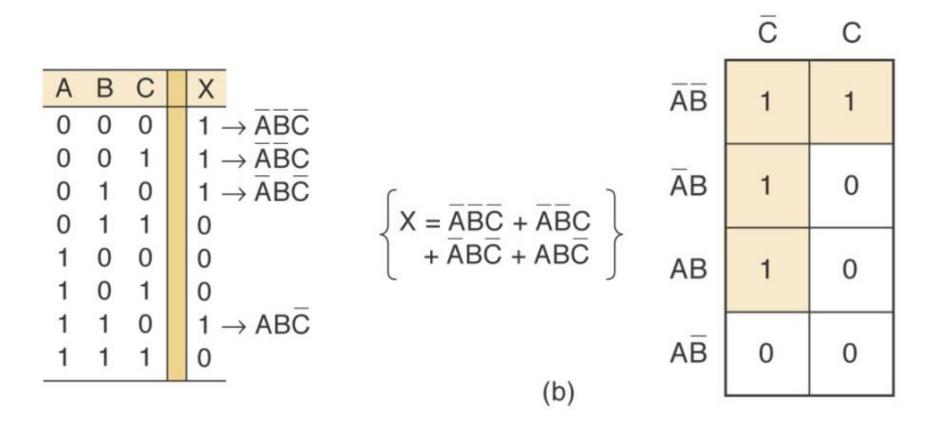

° Three variable maps.

#### F = A'B'C + A'BC' + AB'C' + AB'C + ABC' + ABC

Sum of Products expression (SOP)

| Α | B | С | F |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

F = A'B'C + A'BC' + AB'C' + AB'C + ABC' + ABC

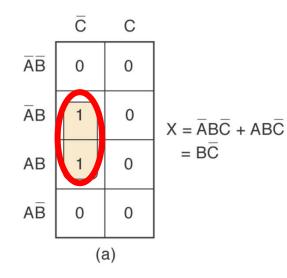

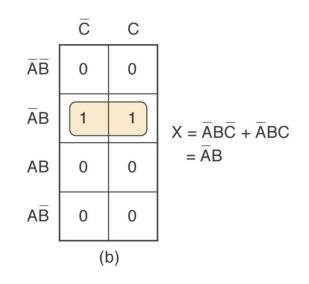

## **Rules for K-Maps**

- We can reduce functions by circling 1's in the K-map

- Each circle represents min-term reduction

- Following circling, we can deduce minimized and-or form.

#### Rules to consider

- Every cell containing a 1 must be included at least once.

- The largest possible "power of 2 rectangle" must be enclosed.

- The 1's must be enclosed in the smallest possible number of rectangles.

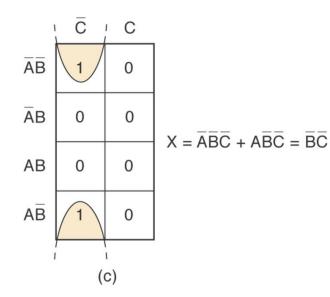

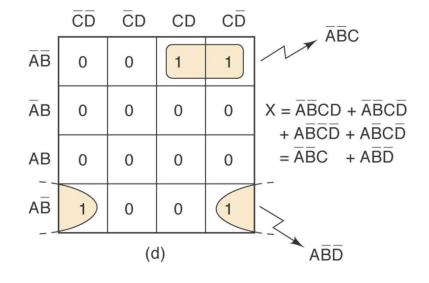

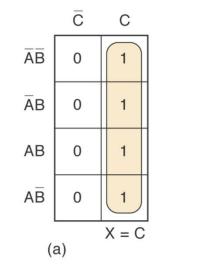

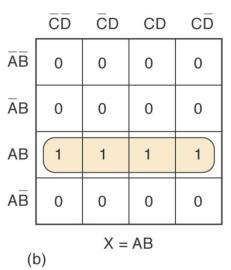

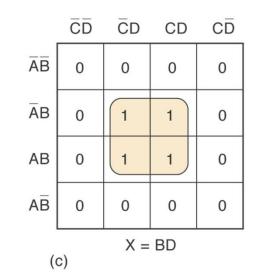

#### K-Maps and truth tables for (a) two variables.

#### K-Maps and truth tables for (b) three variables.

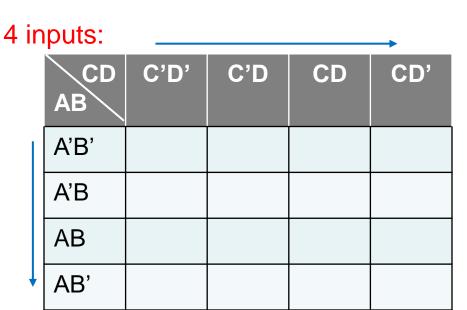

#### K-Maps and truth tables for (c) four variables.

| ABCD    | X                                                                                                                                                                                                                  |    |      |    |    |    |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|------|----|----|----|

| 0 0 0 0 | 0                                                                                                                                                                                                                  |    | ĈD   | ĈD | CD | ĈD |

| 0 0 0 1 | $1 \rightarrow ABCD$                                                                                                                                                                                               |    |      |    |    |    |

| 0 0 1 0 | 0                                                                                                                                                                                                                  | AB | 0    | 1  | 0  | 0  |

| 0 0 1 1 | 0                                                                                                                                                                                                                  |    |      |    |    |    |

| 0 1 0 0 |                                                                                                                                                                                                                    | ĀΒ | 0    | 1  | 0  | 0  |

| 0 1 0 1 | $ \begin{array}{c} 1 \rightarrow \overline{A}B\overline{C}D \\ 0 \end{array} $ $ \begin{array}{c} X = \overline{A}\overline{B}\overline{C}D + \overline{A}B\overline{C}D \\ + AB\overline{C}D + ABCD \end{array} $ |    | 0    |    | Ŭ  | Ŭ  |

| 0 1 1 0 | $0 + AB\overline{C}D + ABCD$                                                                                                                                                                                       |    |      |    |    |    |

| 0 1 1 1 | 0                                                                                                                                                                                                                  | AB | 0    | 1  | 1  | 0  |

| 1 0 0 0 | 0                                                                                                                                                                                                                  |    |      |    |    |    |

| 1001    | 0                                                                                                                                                                                                                  | AB | 0    | 0  | 0  | 0  |

| 1010    | 0                                                                                                                                                                                                                  |    | 1922 |    |    |    |

| 1011    | 0                                                                                                                                                                                                                  |    |      |    |    |    |

| 1 1 0 0 | 0                                                                                                                                                                                                                  |    |      |    |    |    |

| 1 1 0 1 | $1 \rightarrow ABCD$                                                                                                                                                                                               |    |      |    |    |    |

| 1 1 1 0 | 0                                                                                                                                                                                                                  |    |      |    |    |    |

| 1 1 1 1 | $1 \rightarrow ABCD$                                                                                                                                                                                               |    |      |    |    |    |

## Karnaugh Map Method

- Loop adjacent groups of 2, 4, or 8 that contain 1's will result in further simplification.

- When the largest possible groups have been looped, only the common terms are placed in the final expression.

- Looping may also be wrapped between top, bottom, and sides.

#### Looping pairs of adjacent 1's – One variable is eliminated.

#### Looping groups of four adjacent 1's – Two variables are eliminated.

## **Complete K-Map simplification process**

- 1. Construct the K map, place 1s as per the truth table.

- 2. Loop 1s that are not adjacent to any other 1s.

- 3. Loop 1s that are in pairs and cannot be looped into quads or octets.

- 4. Loop 1s in octets (8) even if they have already been looped.

- 5. Loop quads (4) that have one or more 1s not already looped.

- 6. Loop any pairs (2) necessary to include 1s not already looped.

- 7. Form the OR sum of terms generated by each loop.

## Simplify the following Boolean expression: $\overline{A}\overline{B}C\overline{D} + \overline{A}B\overline{C}D + \overline{A}BCD + AB\overline{C}D + ABCD + A\overline{B}CD$

## Simplify the following Boolean expression: $\overline{ABCD} + \overline{ABCD} + \overline{ABCD} + AB\overline{CD} + ABCD + A\overline{B}CD$

|    | ĊD | ĊD | CD | СD |

|----|----|----|----|----|

| ĀB |    |    |    |    |

| ĀB |    |    |    |    |

| AB |    |    |    |    |

| AB |    |    |    |    |

1. Construct the K map, place 1s as per the truth table.

- 2. Loop 1s that are not adjacent to any other 1s.

- 3. Loop 1s that are in pairs and cannot be looped into quads or octets.

- 4. Loop 1s in octets (8) even if they have already been looped.

- 5. Loop quads (4) that have one or more 1s not already looped.

- 6. Loop any pairs (2) necessary to *include 1s not already looped.*

- 7. Form the OR sum of terms generated by each loop.

## Simplify the following Boolean expression: $\overline{ABCD} + \overline{ABCD} + \overline{ABCD} + AB\overline{CD} + A\overline{BCD}$

|    | ĊD | ĊD | CD | СD |

|----|----|----|----|----|

| ĀB |    |    |    | 1  |

| ĀB |    | 1  | 1  |    |

| AB |    | 1  | 1  |    |

| AB |    |    | 1  |    |

#### 1. Construct the K map, place 1s as per the truth table.

- 2. Loop 1s that are not adjacent to any other 1s.

- 3. Loop 1s that are in pairs *and cannot be looped into quads or octets.*

- 4. Loop 1s in octets (8) *even if they have already been looped.*

- 5. Loop quads (4) that have one or more 1s not already looped.

- 6. Loop any pairs (2) necessary to *include 1s not already looped.*

- 7. Form the OR sum of terms generated by each loop.

## Simplify the following Boolean expression: $\overline{ABCD} + \overline{ABCD} + \overline{ABCD} + AB\overline{CD} + A\overline{BCD}$

|    | ĊD | ĊD | CD | СD |

|----|----|----|----|----|

| ĀB |    |    |    |    |

| ĀB |    | 1  | 1  |    |

| AB |    | 1  | 1  |    |

| AB |    |    | 1  |    |

1. Construct the K map, place 1s as per the truth table.

#### 2. Loop 1s that are not adjacent to any other 1s.

- 3. Loop 1s that are in pairs *and cannot be looped into quads or octets.*

- 4. Loop 1s in octets (8) even if they have already been looped.

- 5. Loop quads (4) that have one or more 1s not already looped.

- 6. Loop any pairs (2) necessary to *include 1s not already looped.*

- 7. Form the OR sum of terms generated by each loop.

## Simplify the following Boolean expression: $\overline{ABCD} + \overline{ABCD} + \overline{ABCD} + AB\overline{CD} + ABCD + A\overline{B}CD$

|    | ĊD | ĒD | CD | СD |

|----|----|----|----|----|

| ĀB |    |    |    |    |

| ĀB |    | 1  | 1  |    |

| AB |    | 1  |    |    |

| AB |    |    |    |    |

1. Construct the K map, place 1s as per the truth table.

- 2. Loop 1s that are not adjacent to any other 1s.

- 3. Loop 1s that are in pairs and cannot be looped into quads or octets.

- 4. Loop 1s in octets (8) *even if they have already been looped.*

- 5. Loop quads (4) that have one or more 1s not already looped.

- 6. Loop any pairs (2) necessary to *include 1s not already looped.*

- 7. Form the OR sum of terms generated by each loop.

## Simplify the following Boolean expression: $\overline{ABCD} + \overline{ABCD} + \overline{ABCD} + AB\overline{CD} + A\overline{BCD}$

|    | ĊD | ĒD | CD | СD |

|----|----|----|----|----|

| ĀB |    |    |    |    |

| ĀB |    | 1  | 1  |    |

| AB |    | 1  |    |    |

| AB |    |    |    |    |

1. Construct the K map, place 1s as per the truth table.

- 2. Loop 1s that are not adjacent to any other 1s.

- 3. Loop 1s that are in pairs *and cannot be looped into quads or octets.*

- 4. Loop 1s in octets (8) even if they have already been looped. (none here)

- 5. Loop quads (4) that have one or more 1s not already looped.

- 6. Loop any pairs (2) necessary to *include 1s not already looped.*

- 7. Form the OR sum of terms generated by each loop.

# Example (a) K-Map simplification

# Simplify the following Boolean expression: $\overline{ABCD} + \overline{ABCD} + \overline{ABCD} + AB\overline{CD} + A\overline{BCD}$

|    | <b>D</b> | ĒD | CD | СD |

|----|----------|----|----|----|

| ĀB |          |    |    |    |

| ĀB |          | 1  | 1  |    |

| AB |          | 1  | 1  |    |

| AB |          |    |    |    |

1. Construct the K map, place 1s as per the truth table.

- 2. Loop 1s that are not adjacent to any other 1s.

- 3. Loop 1s that are in pairs *and cannot be looped into quads or octets.*

- 4. Loop 1s in octets (8) *even if they have already been looped.*

- 5. Loop quads (4) that have one or more 1s not already looped.

- 6. Loop any pairs (2) necessary to *include 1s not already looped.*

- 7. Form the OR sum of terms generated by each loop.

# Example 1: K-Map simplification

# Simplify the following Boolean expression: $\overline{ABCD} + \overline{ABCD} + \overline{ABCD} + AB\overline{CD} + A\overline{BCD}$

|    | ĊD | ĒD | CD | CD |

|----|----|----|----|----|

| ĀB |    |    |    |    |

| ĀB |    | 1  | 1  |    |

| AB |    | 1  | 1  |    |

| AB |    |    |    |    |

1. Construct the K map, place 1s as per the truth table.

- 2. Loop 1s that are not adjacent to any other 1s.

- 3. Loop 1s that are in pairs and cannot be looped into quads or octets.

- 4. Loop 1s in octets (8) *even if they have already been looped.*

- 5. Loop quads (4) that have one or more 1s not already looped.

- 6. Loop any pairs (2) necessary to *include 1s not already looped. (none here)*

- 7. Form the OR sum of terms generated by each loop.

# Example 1: K-Map simplification

# Simplify the following Boolean expression: $\overline{ABCD} + \overline{ABCD} + \overline{ABCD} + AB\overline{CD} + ABCD + A\overline{B}CD$

|    | ĊD | ĊD | CD | сБ |

|----|----|----|----|----|

| ĀB |    |    |    |    |

| ĀB |    | 1  | 1  |    |

| AB |    | 1  | 1  |    |

| AB |    |    |    |    |

BD + ACD + ABCD

1. Construct the K map, place 1s as per the truth table.

- 2. Loop 1s that are not adjacent to any other 1s.

- 3. Loop 1s that are in pairs and cannot be looped into quads or octets.

- 4. Loop 1s in octets (8) *even if they have already been looped.*

- 5. Loop quads (4) that have one or more 1s not already looped.

- 6. Loop any pairs (2) necessary to *include 1s not already looped.*

- 7. Form the OR sum of terms generated by each loop.

Use a K-map to simplify:

# $y = \overline{C}(\overline{A}\overline{B}\overline{D} + D) + A\overline{B}C + \overline{D}$

$$y = \overline{C}(\overline{A}\overline{B}\overline{D} + D) + A\overline{B}C + \overline{D}$$

$y = \overline{A}\overline{B}\overline{C}\overline{D} + \overline{C}D + A\overline{B}C + \overline{D} = A'B'C'D'+C'D+AB'C+D'$

$y = C(\overline{A}\overline{B}\overline{D} + D) + A\overline{B}C + \overline{D}$

### $\mathbf{y} = \overline{\mathbf{A}}\overline{\mathbf{B}}\overline{\mathbf{C}}\overline{\mathbf{D}} + \overline{\mathbf{C}}\mathbf{D} + \mathbf{A}\overline{\mathbf{B}}\mathbf{C} + \overline{\mathbf{D}} = \mathbf{A}'\mathbf{B}'\mathbf{C}'\mathbf{D}' + \mathbf{C}'\mathbf{D} + \mathbf{A}\mathbf{B}'\mathbf{C} + \mathbf{D}'$

|                             | CD<br>AB | C'D' | C'D | CD | CD' |

|-----------------------------|----------|------|-----|----|-----|

| <u>Step 1:</u><br>Draw Kmap | A'B'     |      |     |    |     |

|                             | A'B      |      |     |    |     |

|                             | AB       |      |     |    |     |

|                             | AB'      |      |     |    |     |

$y = C(\overline{A}BD + D) + ABC + D$

$\mathbf{y} = \overline{\mathbf{A}}\overline{\mathbf{B}}\overline{\mathbf{C}}\overline{\mathbf{D}} + \overline{\mathbf{C}}\mathbf{D} + \overline{\mathbf{A}}\overline{\mathbf{B}}\mathbf{C} + \overline{\mathbf{D}} = \mathbf{A}'\mathbf{B}'\mathbf{C}'\mathbf{D}' + \mathbf{C}'\mathbf{D} + \mathbf{A}\mathbf{B}'\mathbf{C} + \mathbf{D}'$

| AB CD | C'D' | C'D | CD | CD' |

|-------|------|-----|----|-----|

| A'B'  | 1    |     |    |     |

| A'B   |      |     |    |     |

| AB    |      |     |    |     |

| AB'   |      |     |    |     |

$y = C(\overline{A}BD + D) + ABC + D$

#### $\mathbf{y} = \overline{\mathbf{A}}\overline{\mathbf{B}}\overline{\mathbf{C}}\overline{\mathbf{D}} + \overline{\mathbf{C}}\mathbf{D} + \overline{\mathbf{A}}\overline{\mathbf{B}}\mathbf{C} + \overline{\mathbf{D}} = \mathbf{A'B'C'D'} + \mathbf{C'D'} + \mathbf{AB'C'D'}$

| AB CD | C'D' | C'D | CD | CD' |

|-------|------|-----|----|-----|

| A'B'  | 1    | 1   |    |     |

| A'B   |      | 1   |    |     |

| AB    |      | 1   |    |     |

| AB'   |      | 1   |    |     |

$y = C(\overline{A}BD + D) + ABC + D$

#### $\mathbf{y} = \overline{\mathbf{A}}\overline{\mathbf{B}}\overline{\mathbf{C}}\overline{\mathbf{D}} + \overline{\mathbf{C}}\mathbf{D} + \overline{\mathbf{A}}\overline{\mathbf{B}}\mathbf{C} + \overline{\mathbf{D}} = \mathbf{A}'\mathbf{B}'\mathbf{C}'\mathbf{D}' + \mathbf{C}'\mathbf{D} + \mathbf{A}\mathbf{B}'\mathbf{C} + \mathbf{D}'$

| AB CD | C'D' | C'D | CD | CD' |

|-------|------|-----|----|-----|

| A'B'  | 1    | 1   |    |     |

| A'B   |      | 1   |    |     |

| AB    |      | 1   |    |     |

| AB'   |      | 1   | 1  | 1   |

$y = C(\overline{A}BD + D) + ABC + D$

#### $\mathbf{y} = \overline{\mathbf{A}}\overline{\mathbf{B}}\overline{\mathbf{C}}\overline{\mathbf{D}} + \overline{\mathbf{C}}\mathbf{D} + \mathbf{A}\overline{\mathbf{B}}\mathbf{C} + \overline{\mathbf{D}} = \mathbf{A}'\mathbf{B}'\mathbf{C}'\mathbf{D}' + \mathbf{C}'\mathbf{D} + \mathbf{A}\mathbf{B}'\mathbf{C} + \mathbf{D}'$

| AB CD | C' <b>D'</b> | C'D |   | С <b>D</b> ' |

|-------|--------------|-----|---|--------------|

| A'B'  | 1            | 1   |   | 1            |

| A'B   | 1            | 1   |   | 1            |

| AB    | 1            | 1   |   | 1            |

| AB'   | 1            | 1   | 1 | 1            |

$y = C(\overline{A}BD + D) + ABC + D$

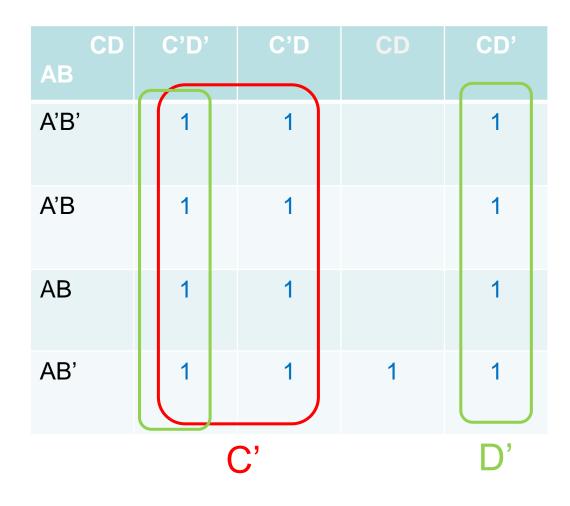

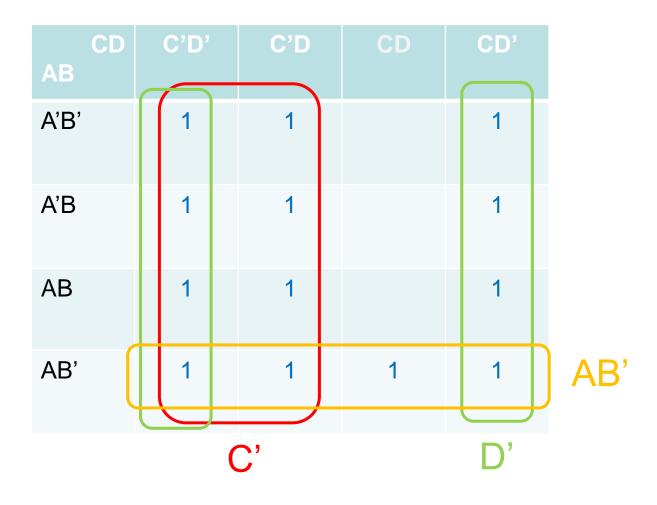

$\mathbf{y} = \overline{\mathbf{A}}\overline{\mathbf{B}}\overline{\mathbf{C}}\overline{\mathbf{D}} + \overline{\mathbf{C}}\mathbf{D} + \mathbf{A}\overline{\mathbf{B}}\mathbf{C} + \overline{\mathbf{D}} = \mathbf{A}'\mathbf{B}'\mathbf{C}'\mathbf{D}' + \mathbf{C}'\mathbf{D} + \mathbf{A}\mathbf{B}'\mathbf{C} + \mathbf{D}'$

Step 3: Loop 1s in a pair, or in a quad, or in an octet

| CD<br>AB | C'D' | C'D | CD | CD' |

|----------|------|-----|----|-----|

| A'B'     | 1    | 1   |    | 1   |

| A'B      | 1    | 1   |    | 1   |

| AB       | 1    | 1   |    | 1   |

| AB'      | 1    | 1   | 1  | 1   |

|          | (    | C'  |    |     |

$y = C(\overline{A}\overline{B}\overline{D} + D) + A\overline{B}C + \overline{D}$

$y = \overline{A}\overline{B}\overline{C}\overline{D} + \overline{C}D + A\overline{B}C + \overline{D} = A'B'C'D'+C'D+AB'C+D'$

Step 3: Loop 1s in a pair, or in a quad, or in an octet

$y = C(\overline{A}\overline{B}\overline{D} + D) + A\overline{B}C + \overline{D}$

$y = \overline{A}\overline{B}\overline{C}\overline{D} + \overline{C}D + A\overline{B}C + \overline{D} = A'B'C'D'+C'D+AB'C+D'$

Step 3: Loop 1s in a pair, or in a quad, or in an octet

$y = C(\overline{A}BD + D) + ABC + D$

# $y = \overline{ABCD} + \overline{CD} + \overline{ABC} + \overline{D} = A'B'C'D' + C'D + AB'C + D'$ = AB' + C' + D'

<u>Step 4:</u> Write the OR sum of terms

- Simpify the following expressions

- using Boolean algebra and

- using K-maps

(a)

$$x = \overline{A}\overline{B}\overline{C} + \overline{A}BC + ABC + A\overline{B}\overline{C} + A\overline{B}C$$

(b)  $x = \overline{C + D} + \overline{A}C\overline{D} + A\overline{B}\overline{C} + \overline{A}\overline{B}CD + AC\overline{D}$

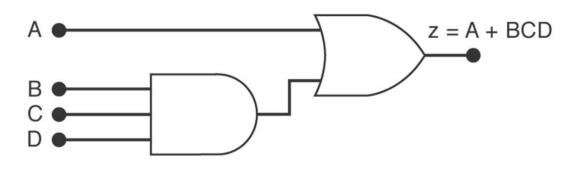

#### **Designing Combinational Logic Circuits**

If we know the design conditions {(a) truth table} we want to design the logic circuit and then (b) implement the circuit with AND, OR and NOT gates.

#### Designing Combinational Logic Circuits

#### **Design Procedure:**

- 1. Set up truth table

- 2. Write AND term for each case where the output is HI

- 3. Write the SOP expression for the output

- 4. Simplify the expression

- 5. Implement the circuit

## **Designing Combinational Logic Circuits**

#### Example 1:

Design a logic circuit that has three inputs, *A*, *B*, and *C*, whose output will be HIGH only when a majority of the inputs are HIGH.

#### 1) Set up truth table

Design a logic circuit that has <u>three inputs</u>, *A*, *B*, and *C*, whose output will be HIGH only when a majority of the inputs are HIGH.

#### 1) Set up truth table

Design a logic circuit that has three inputs, A, B, and C, whose output will be HIGH only when a majority of the inputs are HIGH.

2) Write AND term for each case where the output is HI

| A | B | С | x |                              |

|---|---|---|---|------------------------------|

| 0 | 0 | 0 | 0 |                              |

| 0 | 0 | 1 | 0 |                              |

| 0 | 1 | 0 | 0 |                              |

| 0 | 1 | 1 | 1 | $\rightarrow \overline{A}BC$ |

| 1 | 0 | 0 | 0 |                              |

| 1 | 0 | 1 | 1 | $\rightarrow A\overline{B}C$ |

| 1 | 1 | 0 | 1 | $\rightarrow AB\overline{C}$ |

| 1 | 1 | 1 | 1 | $\rightarrow ABC$            |

#### 3) Write the SOP expression for the output

#### $x = \overline{ABC} + A\overline{BC} + AB\overline{C} + ABC$

4) Simplify the expression – using Boolean Algebra Laws

$$x = \overline{ABC} + A\overline{BC} + AB\overline{C} + ABC$$

$$x = \overline{ABC} + ABC + A\overline{BC} + ABC + AB\overline{C} + ABC$$

$$x = BC(\overline{A} + A) + AC(\overline{B} + B) + AB(\overline{C} + C)$$

$$x = BC + AC + AB$$

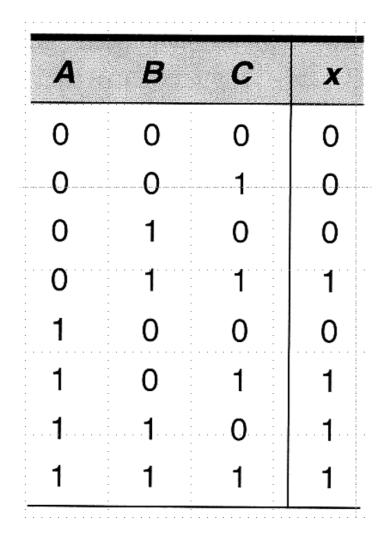

4) Simplify the expression – using K-Map method

#### X = A'BC + AB'C + ABC' + ABC

|      | C' | С |

|------|----|---|

| A'B' |    |   |

| A'B  |    | 1 |

| AB   | 1  | 1 |

| AB'  |    | 1 |

4) Simplify the expression – using K-Map method

#### X = A'BC + AB'C + ABC' + ABC

Simplified expression is AB + BC + AC

- 3) Write the SOP expression for the output

- 4) Simplified the expression: x = BC + AC + AB

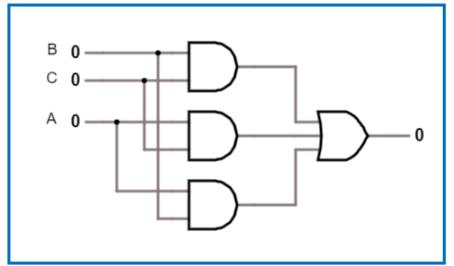

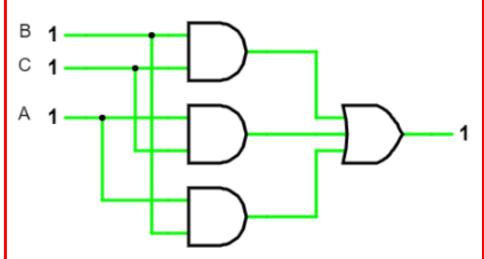

5) Implement circuit:

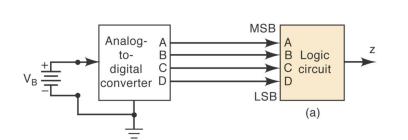

#### Example 3:

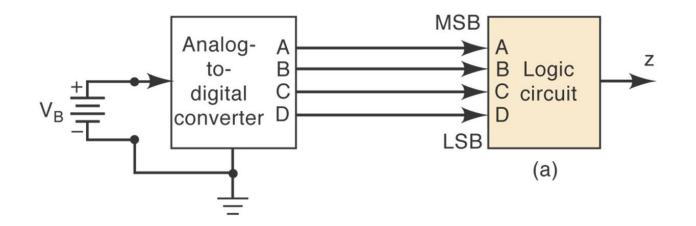

Design a battery monitor that will produce a HI (ie 1) so long as the battery is higher than 6 V (= 0110 in binary) on the output of the ADC (Analog to Digital Converter)

Step 1: Set up the Truth Table

|    | Α | В | С | D | z |

|----|---|---|---|---|---|

| 0  | 0 | 0 | 0 | 0 |   |

| 1  | 0 | 0 | 0 | 1 |   |

| 2  | 0 | 0 | 1 | 0 |   |

| 3  | 0 | 0 | 1 | 1 |   |

| 4  | 0 | 1 | 0 | 0 |   |

| 5  | 0 | 1 | 0 | 1 |   |

| 6  | 0 | 1 | 1 | 0 |   |

| 7  | 0 | 1 | 1 | 1 |   |

| 8  | 1 | 0 | 0 | 0 |   |

| 9  | 1 | 0 | 0 | 1 |   |

| 10 | 1 | 0 | 1 | 0 |   |

| 11 | 1 | 0 | 1 | 1 |   |

| 12 | 1 | 1 | 0 | 0 |   |

| 13 | 1 | 1 | 0 | 1 |   |

| 14 | 1 | 1 | 1 | 0 |   |

| 15 | 1 | 1 | 1 | 1 |   |

**Example 3:** Design a battery monitor that will produce a HI

so long as the battery is higher than 6 V = 0110 on the output of the ADC (Analog to Digital Converter)

Step 1: Set up the Truth Table

|    | Α | В | С | D | Z |

|----|---|---|---|---|---|

| 0  | 0 | 0 | 0 | 0 |   |

| 1  | 0 | 0 | 0 | 1 |   |

| 2  | 0 | 0 | 1 | 0 |   |

| 3  | 0 | 0 | 1 | 1 |   |

| 4  | 0 | 1 | 0 | 0 |   |

| 5  | 0 | 1 | 0 | 1 |   |

| 6  | 0 | 1 | 1 | 0 |   |

| 7  | 0 | 1 | 1 | 1 | 1 |

| 8  | 1 | 0 | 0 | 0 | 1 |

| 9  | 1 | 0 | 0 | 1 | 1 |

| 10 | 1 | 0 | 1 | 0 | 1 |

| 11 | 1 | 0 | 1 | 1 | 1 |

| 12 | 1 | 1 | 0 | 0 | 1 |

| 13 | 1 | 1 | 0 | 1 | 1 |

| 14 | 1 | 1 | 1 | 0 | 1 |

| 15 | 1 | 1 | 1 | 1 | 1 |

| Step 1: Set up the Truth Table                      |    | Α | В | С | D | z                 |

|-----------------------------------------------------|----|---|---|---|---|-------------------|

|                                                     | 0  | 0 | 0 | 0 | 0 |                   |

|                                                     | 1  | 0 | 0 | 0 | 1 |                   |

| Analog- A<br>to- B B Logic z                        | 2  | 0 | 0 | 1 | 0 |                   |

| V <sub>B</sub> + C circuit<br>converter D C circuit | 3  | 0 | 0 | 1 | 1 |                   |

|                                                     | 4  | 0 | 1 | 0 | 0 |                   |

| <u>+</u>                                            | 5  | 0 | 1 | 0 | 1 |                   |

|                                                     | 6  | 0 | 1 | 1 | 0 |                   |

|                                                     | 7  | 0 | 1 | 1 | 1 | 1 → A'E           |

| Step 2: Write AND term for                          | 8  | 1 | 0 | 0 | 0 | 1 <del>→</del> AB |

| each case where the output is                       | 9  | 1 | 0 | 0 | 1 | 1 <del>→</del> AB |

| HI                                                  | 10 | 1 | 0 | 1 | 0 | 1 <del>→</del> AB |

|                                                     | 11 | 1 | 0 | 1 | 1 | 1 <del>→</del> AB |

|                                                     | 12 | 1 | 1 | 0 | 0 | 1 <del>→</del> AB |

|                                                     | 13 | 1 | 1 | 0 | 1 | 1 <del>→</del> AB |

|                                                     | 14 | 1 | 1 | 1 | 0 | 1 <del>→</del> AB |

|                                                     | 15 | 1 | 1 | 1 | 1 | 1 → AB            |

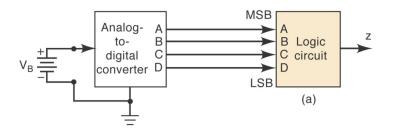

<u>Step 1</u>: Set up the Truth Table

Step 2: Write AND term for each case where the output is HI

Step 3: Write the SOP for the output

z = A'BCD + AB'C'D' + AB'C'D+ AB'CD' + AB'CD + ABC'D' +ABC'D + ABCD' + ABCD

|    | Α | В | С | D | z |                    |

|----|---|---|---|---|---|--------------------|

| 0  | 0 | 0 | 0 | 0 |   |                    |

| 1  | 0 | 0 | 0 | 1 |   |                    |

| 2  | 0 | 0 | 1 | 0 |   |                    |

| 3  | 0 | 0 | 1 | 1 |   |                    |

| 4  | 0 | 1 | 0 | 0 |   |                    |

| 5  | 0 | 1 | 0 | 1 |   |                    |

| 6  | 0 | 1 | 1 | 0 |   |                    |

| 7  | 0 | 1 | 1 | 1 | 1 | A'BCD              |

| 8  | 1 | 0 | 0 | 0 | 1 | AB'C'D'            |

| 9  | 1 | 0 | 0 | 1 | 1 | AB'C'D             |

| 10 | 1 | 0 | 1 | 0 | 1 | AB'CD'             |

| 11 | 1 | 0 | 1 | 1 | 1 | AB'CD              |

| 12 | 1 | 1 | 0 | 0 | 1 | ABC'D'             |

| 13 | 1 | 1 | 0 | 1 | 1 | ABC'D              |

| 14 | 1 | 1 | 1 | 0 | 1 | ABCD'              |

| 15 | 1 | 1 | 1 | 1 | 1 | ABCD <sub>67</sub> |

Step 3: Write the SOP for the output

z = A'BCD + AB'C'D' + AB'C'D+ AB'CD' + AB'CD + ABC'D' +ABC'D + ABCD' + ABCD

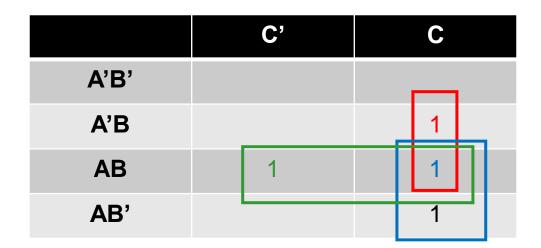

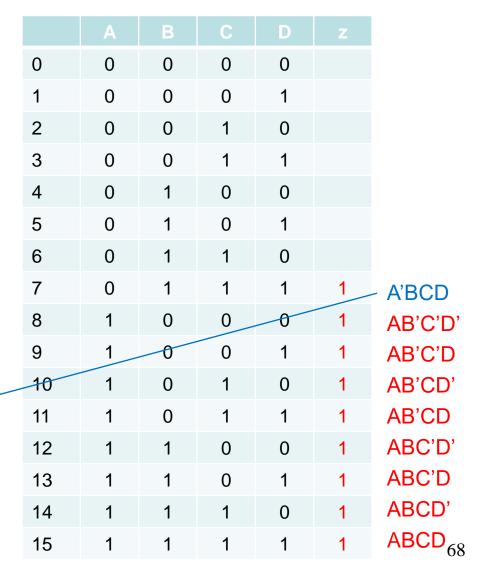

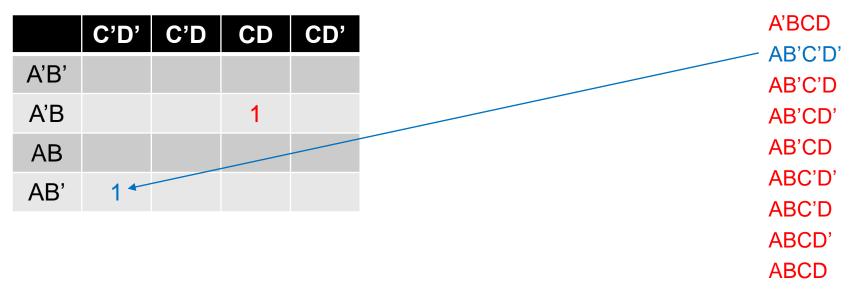

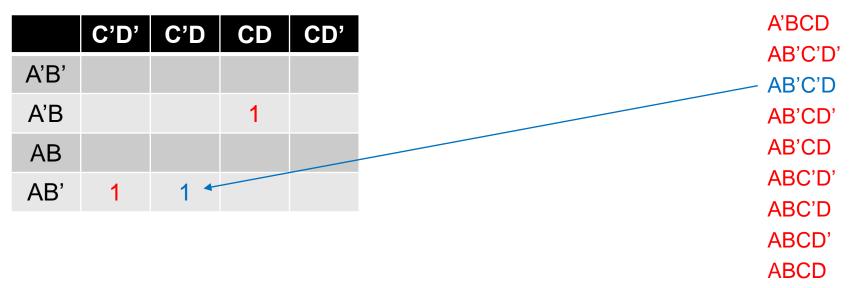

Step 4: Simplify the expression

|      | C'D' | C'D | CD  | CD' |

|------|------|-----|-----|-----|

| A'B' |      |     |     |     |

| A'B  |      |     | 1 - |     |

| AB   |      |     |     |     |

| AB'  |      |     |     |     |

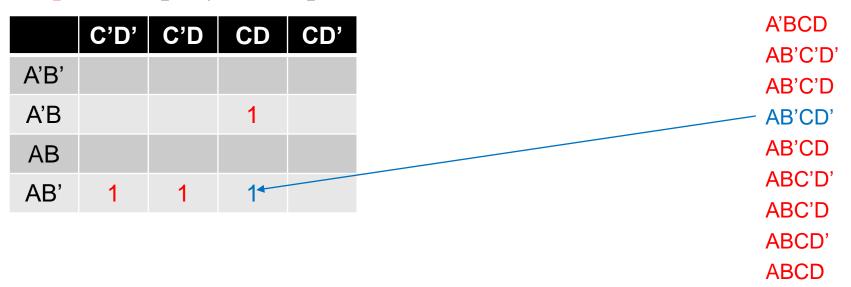

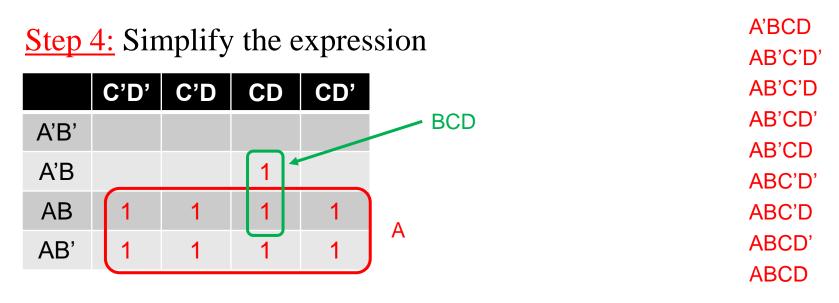

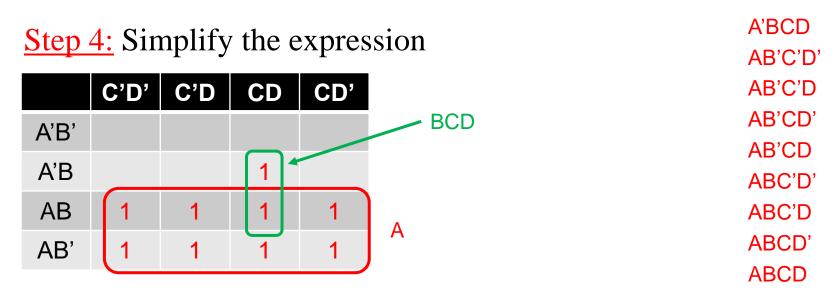

<u>Step 4:</u> Simplify the expression

<u>Step 4:</u> Simplify the expression

<u>Step 4:</u> Simplify the expression

<u>Step 4:</u> Simplify the expression

|      | C'D' | C'D | CD | CD' |

|------|------|-----|----|-----|

| A'B' |      |     |    |     |

| A'B  |      |     | 1  |     |

| AB   | 1    | 1   | 1  | 1   |

| AB'  | 1    | 1   | 1  | 1   |

A'BCD AB'C'D' AB'CD' AB'CD' AB'CD ABC'D' ABC'D ABCD'

#### Simplified expression is BCD + A

<u>Step 5:</u> Implement the logic circuit

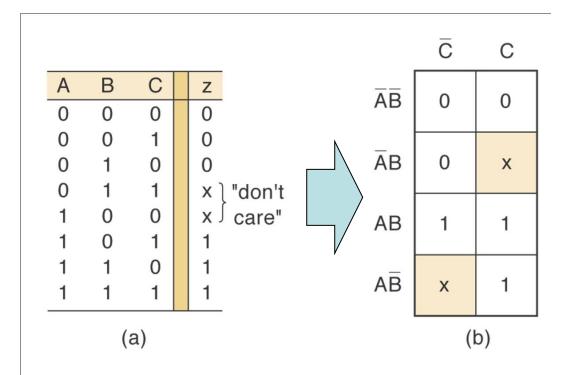

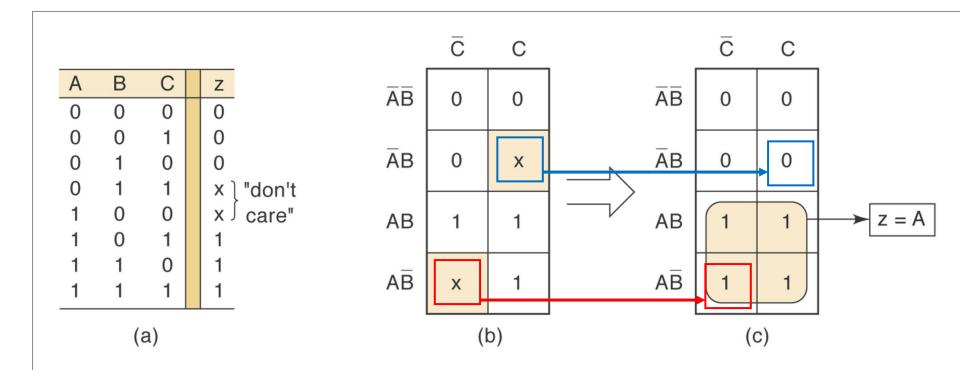

# **Don't care Output Conditions**

In some cases, we may encounter output states that are 'impossible' – that is the corresponding input combination is not possible in practice

Eg: A digital display (0-9) that is driven by a binary input (4 bits): binary values 1010 -> 1111 never occur.

# **Don't care Output Conditions**

Can be changed 0/1 so that the simplest expression can be obtained from the K-map. Typically occur when we know certain input conditions are impossible.

# **Don't care Output Conditions**

Can be changed 0/1 so that the simplest expression can be obtained from the K-map. Typically occur when we know certain input conditions are impossible.

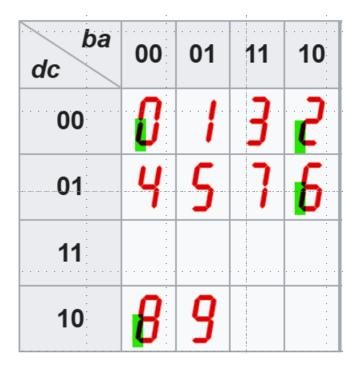

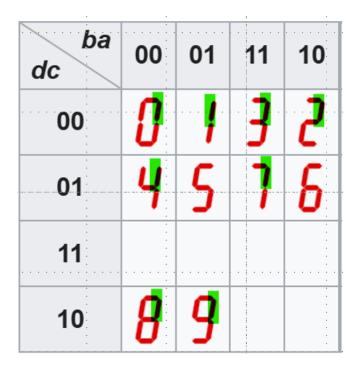

# **Example: Binary Coded Decimal**

Consider again the 4-bit binary number abcd, driving a 7-segment LED display. Simplify the expression that will light up the bottom left led on a 7-segment display.

# **Example: Binary Coded Decimal**

Consider again the 4-bit binary number abcd, driving a 7-segment LED display. Simplify the expression that will light up the bottom left led on a 7-segment display.

| ba<br>dc | 00                                    | 01 | 11 | 10                             | ba<br>dc | 00 | 01 | 11 | 10 | ba<br>dc | 00 | 01 | 11 | 10 |

|----------|---------------------------------------|----|----|--------------------------------|----------|----|----|----|----|----------|----|----|----|----|

| 00       | 0                                     |    | 3  | 2                              | 00       | 1  | 0  | 0  | 1  | 00       | 1  | 0  | 0  | 1  |

| 01       | 4                                     | 5  | 7  | 6                              | 01       | 0  | 0  | 0  | 1  | 01       | 0  | 0  | 0  | 1  |

| 11       | · · · · · · · · · · · · · · · · · · · |    |    | ·<br>·<br>·<br>· · · · · · · · | 11       | х  | х  | x  | х  | 11       | 0  | 0  | 0  | 1  |

| 10       | 8                                     | 9  |    |                                | 10       | 1  | 0  | х  | х  | 10       | 1  | 0  | 0  | 1  |

# **Exercise: Binary Coded Decimal**

Consider again the 4-bit binary number abcd, driving a 7-segment LED display. Simplify the expression that will light up the top right led on a 7-segment display.

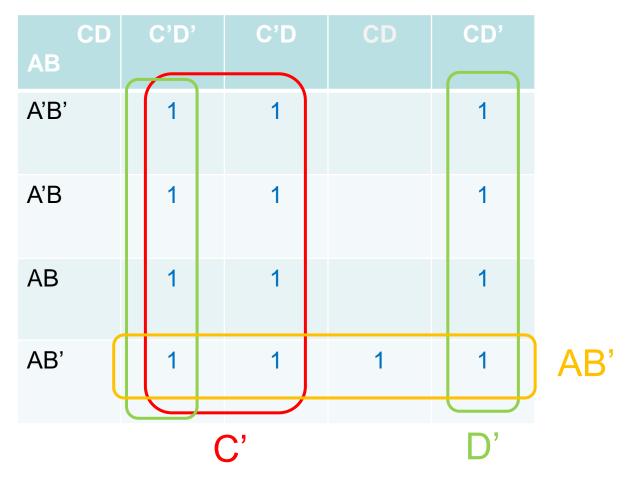

#### Determine the minimum expression for each of the K maps shown below.

|     | ĒÐ | ĒD | CD | CD |    | ĒD  | ĒD | CD | CD |    | Ē   | С |  |

|-----|----|----|----|----|----|-----|----|----|----|----|-----|---|--|

| ĀB  | 1  | 1  | 1  | 1  | ĀB | 1   | 0  | 1  | 1  | ĀB | 0   | 1 |  |

| ĀВ  | 1  | 1  | 0  | 0  | ĀB | 1   | 0  | 0  | 1  | ĀВ | 0   | 0 |  |

| AB  | 0  | 0  | 0  | 1  | AB | 0   | 0  | 0  | 0  | AB | 1   | 0 |  |

| AB  | 0  | 0  | 1  | 1  | AB | 1   | 0  | 1  | 1  | AB | 1   | × |  |

| (a) |    |    |    |    |    | (b) |    |    |    |    | (C) |   |  |

Determine the input conditions needed to produce a HI output in the circuit below