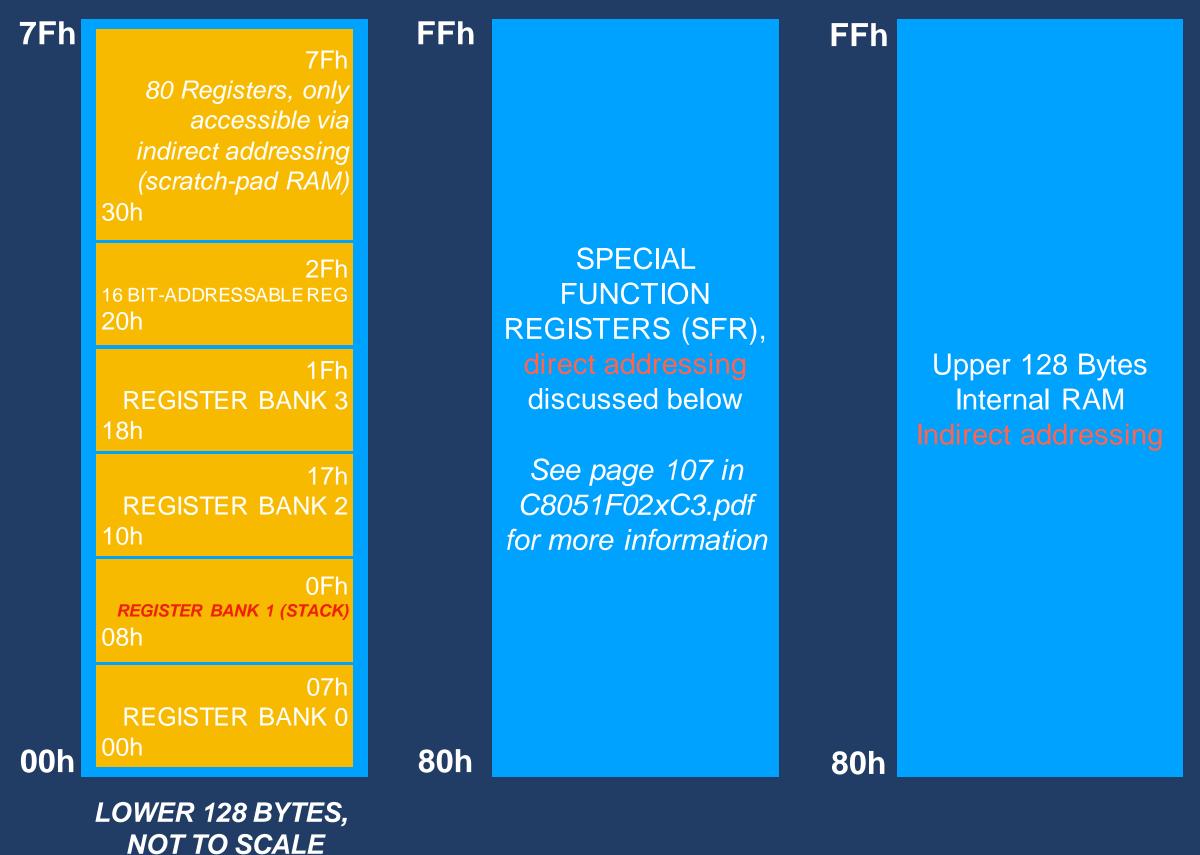

#### 8051 DATA MEMORY MAP

#### 8051 DATA MEMORY MAP

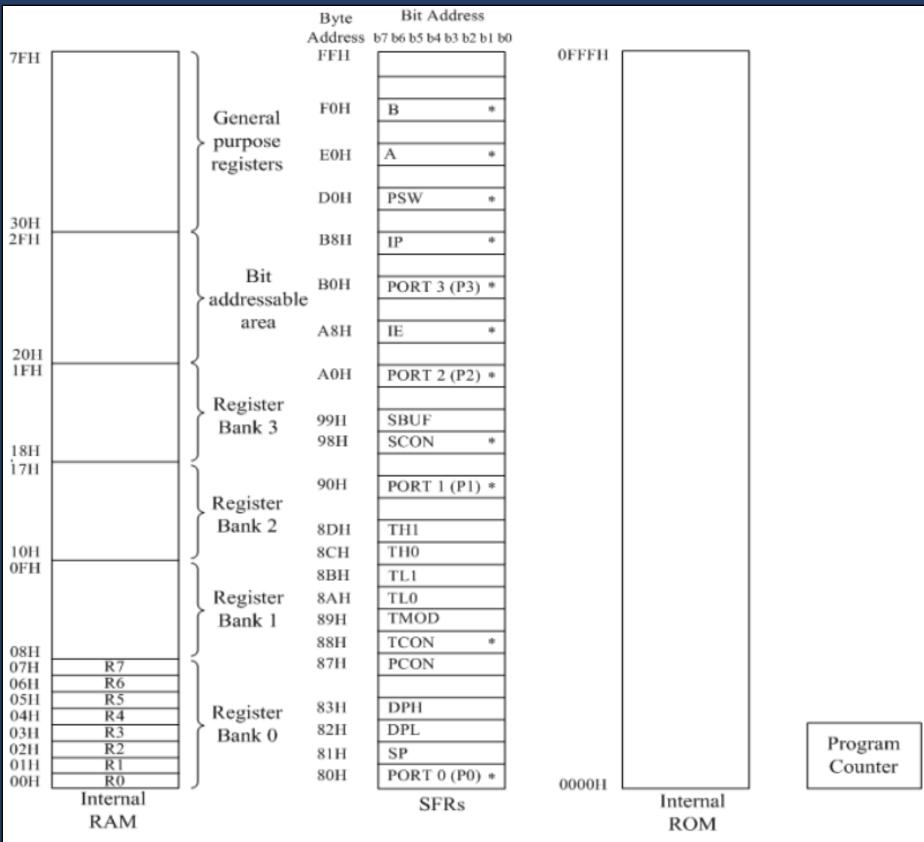

\* Indicates the SFRs which are also bit addressable

#### 8051 ADDRESSING MODES

A key part of computer operation involves the accessing of memory; this may be done on the 8051 using five main approaches.

| • IMMEDIATE<br>ADDRESSING | <ul> <li>REGISTER<br/>ADDRESSING</li> </ul> | <ul> <li>DIRECT<br/>ADDRESSING</li> </ul> | <ul> <li>INDIRECT<br/>ADDRESSING</li> </ul> | <ul> <li>INDEXED<br/>ADDRESSING</li> </ul> |

|---------------------------|---------------------------------------------|-------------------------------------------|---------------------------------------------|--------------------------------------------|

| MODE                      | MODE                                        | MODE                                      | MODE                                        | MODE                                       |

| The data is               | The data                                    | The address of                            | Slower: the                                 | <ul> <li>Used to step</li> </ul>           |

| included in the           | operand is in a                             | a location in                             | contents of a                               | through data                               |

| 8051                      | specified                                   | RAM is                                    | location of the                             | (as in lookup                              |

| instruction.              | register.                                   | specified, and                            | address stored                              | tables).                                   |

| • MOV A,#48H              | <ul> <li>Only some</li> </ul>               | its contents                              | in a register                               | <ul> <li>We won't be</li> </ul>            |

| The # shows               | registers may                               | are operated                              | are fetched.                                | exploring this                             |

| that the data is          | be used: R0                                 | upon. Only                                | <ul> <li>MOV A,@R7</li> </ul>               | in depth (and                              |

| 'immediate'               | through R7 of                               | works with                                | • The @                                     | you won't be                               |

| In a sense, this          | each of the                                 | internal RAM &                            | indicates                                   | tested on it!),                            |

| data is hard-             | 8051's banks.                               | SFR's                                     | an address                                  | but see details                            |

| coded into the            | MOV A,R7                                    | <ul> <li>MOV A,10H</li> </ul>             | Upper 128                                   | about the                                  |

| instruction.              | <ul> <li>Contents of</li> </ul>             | <ul> <li>Contents of</li> </ul>           | bytes of RAM                                | MOVC                                       |

| Fast but less             | R7 are                                      | address                                   | are accessible                              | instruction in                             |

| flexible.                 | copied to                                   | are copied                                | this way.                                   | C8051F02xC3.pdf                            |

|                           | ACC.                                        | to ACC.                                   |                                             |                                            |

|                           |                                             |                                           |                                             |                                            |

# 8051 GENERAL PURPOSE REGISTERS

- The lowest addresses of the 8051's internal RAM are a number of General Purpose Registers.

- There are four banks of these registers, with each bank having 8 registers (R0 through R7).

- 32 Bytes total.

- By default, Bank 0 is enabled.

- As default, MOV A, R7 will move Bank 0's contents to accumulator.

- We can switch register banks using bits 3 and 4 of the PSW flag register.

| R7     | R7     | R7     | R7     |        | RS1 | RS0 |

|--------|--------|--------|--------|--------|-----|-----|

| R6     | R6     | R6     | R6     |        |     |     |

| R5     | R5     | R5     | R5     | BANK 0 | 0   | 0   |

| R4     | R4     | R4     | R4     |        | 0   | 1   |

| R3     | R3     | R3     | R3     | BANK 1 | 0   | 1   |

| R2     | R2     | R2     | R2     | BANK 2 | 1   | 0   |

| R1     | R1     | R1     | R1     |        |     |     |

| R0     | R0     | R0     | R0     | BANK 3 | 1   | 1   |

| Bank 0 | Bank 1 | Bank 2 | Bank 3 |        |     |     |

# 8051 FLAGS

| PSW.7<br>CY<br>(Carry flag,<br>raised<br>when the<br>processor<br>needs to<br>carry in<br>addition) | PSW.6<br>AC<br>(Aux.<br>carry,<br>used<br>during<br>BCD<br>math) | PSW.5<br>F0<br>(User-<br>assignable flag) | PSW.4<br>RS1<br>(Register<br>bank<br>selector,<br>don't<br>worry<br>about for<br>now) | PSW.3<br>RS2<br>(Register<br>bank<br>selector,<br>don't<br>worry<br>about for<br>now) | PWS.2<br>OV<br>(Overflow,<br>raised when a<br>signed number<br>overflows into<br>the sign bit) | PSW.1<br>-<br>(User<br>assignable) | PSW.0<br>P<br>(Parity: 0<br>if acc.<br>holds<br>even<br>number<br>of 1's) |

|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-------------------------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------------------------------------|---------------------------------------------------------------------------|

|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-------------------------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------------------------------------|---------------------------------------------------------------------------|

# GENERAL PURPOSE REGISTER EXAMPLE CODE

MOV R0,#FFH ;Load R0 with 0xFF (immediate addressing) MOV R1,R0 ;Copy R0 contents to R1 (register addressing) MOV P0,R1 ;2 cycles! Direct move from R1 to P0 MOV 00,#FFH ;Address 00 is R0 (direct addressing)

;;Now, we'll switch reg. banks to bank 3 (PSW.4 HI, PSW.3 HI).

SETB PSW.4 ;Sets the register bank select bit RS1 high SETB PSW.3 ;Sets the register bank select bit RS2 high

;;R0-R7 now refer to bank 3 rather than bank 0 (default)

MOV R0,#FFH ;Same operation as top of code, different bank

MOV 00,#FFH ;However, this still refers to `bank 0, R0'