# ECEN202

#### Mohammad Nekooei

#### mohammad.nekooei@vuw.ac.nz

School of Engineering and Computer Science Victoria University of Wellington

## TODAY

- Timers as counters

- Interrupts

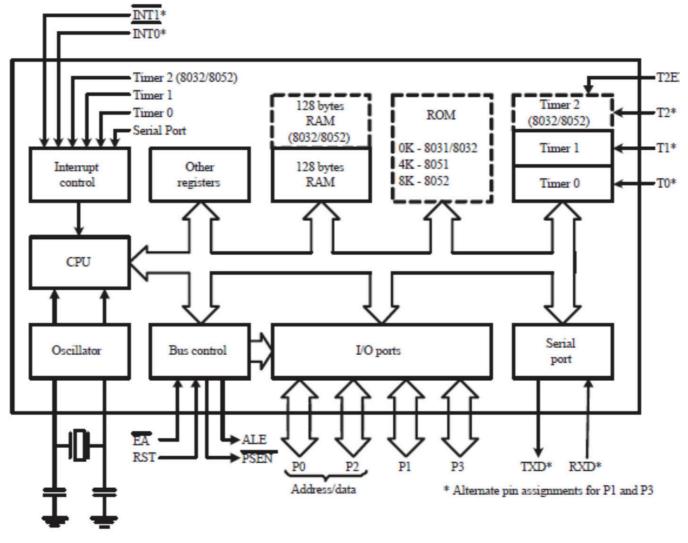

### TIMERS AS COUNTERS

- Timers work by counting events and iterating each time an event arrives.

- In the traditional timer role (as a 'delay generator'), these events come from the microcontroller's crystal oscillator (XTAL).

- We can also configure 8051 timers to count up each time another external event arrives.

- This way, we can count things like button presses, times that sensors have exceeded thresholds, waveform edges, etc.

#### COUNTER EXAMPLE CODE

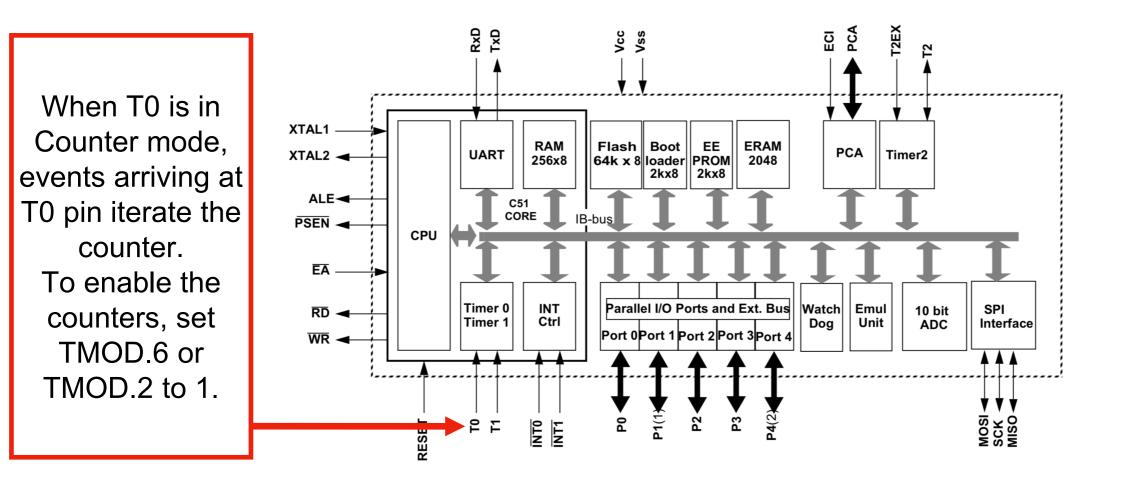

Goal: set up Timer 0 as a counter; count 0-255 (Mode 2) and display this count on Port 2.

PORT 2: LED's connected to each of the port's pins (additional support circuitry not shown)

Events arrive at T0 pin (shares a pin with P3.4; this pin must be set as an input by writing it HIGH)

## TMOD REGISTER

| TMOD.7<br>GATE<br>When 1,<br>timer only<br>counts<br>when TR1<br>bit is high<br>and there is<br>an external<br>interrupt at<br>INT0 | TMOD.6<br>C/T<br>When 0,<br>Timer1<br>serves as<br>XTAL-<br>driven delay<br>generator<br>(timer);<br>When 1,<br>Timer1<br>counts<br>external<br>events | TMOD.5<br>M1<br>Timer 1<br>Mode bit 1<br>(see next<br>slides for<br>timer mode<br>info.) | TMOD.4<br>M0<br>Timer 1<br>Mode bit 0<br>(see next<br>slides for<br>timer mode<br>info.) | TMOD.3<br>GATE<br>When 1,<br>timer only<br>counts<br>when TR0<br>bit is high<br>and there is<br>an external<br>interrupt at<br>INT1 | TMOD.2<br>C/T<br>When 0,<br>Timer0<br>serves as<br>XTAL-<br>driven delay<br>generator<br>(timer);<br>When 1,<br>Timer0<br>counts<br>external<br>events | TMOD.1<br>M1<br>Timer 0<br>Mode bit 1<br>(see next<br>slides for<br>timer mode<br>info.) | TMOD.0<br>M0<br>Timer 0 Mode<br>bit 0 (see next<br>slides for<br>timer mode<br>info.) |

|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

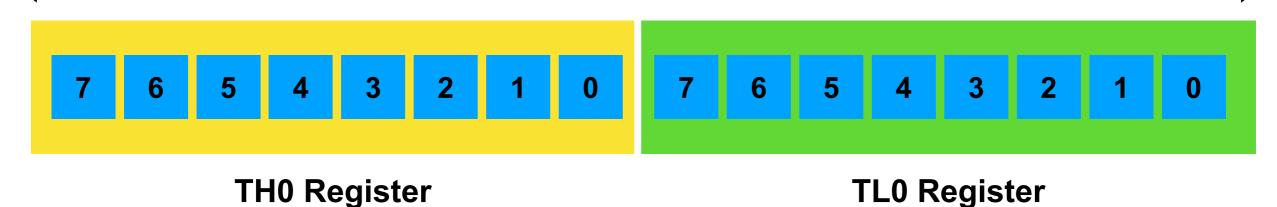

#### 16 Bits: High 8 bits in TH0, Low 8 bits in TL0

#### COUNTER EXAMPLE CODE

MOV TMOD, #00000110B; Set timer 0 as a counter in mode2. MOV THO, #0 ;Clear THO SETB P3.4 ;Set T0 pin (shared with P3.4) to input **START**: ;Start timer 0 SETB TRO LOOP: MOV A, TLO ;Grab how many events TLO holds ;Output the binary count of event numbers MOV P2,A JNB TF0, LOOP ;Keep polling the TLO port as long TFO=0 CLR TRO ;Stop the counter CLR TF0 ;Reset the event arrived flag SJMP START ;Restart the timer, repeat

## WATCHDOG TIMER

- In many critical applications, it can be beneficial to have an "emergency reset" switch.

- This will allow us to reset our microcontroller even if the program hangs up on some routine.

- Useful to let us automatically recover from unexpected 'crashes.'

- Microcontrollers' watchdog timers (WDT's) will automatically reset the system (moving PC to 0, etc.) if they are allowed to overflow.

- In a normally operating system, WDTs are reset in software every so often. If this reset does not occur, then we know that the system is hanging and is in need of a reset.

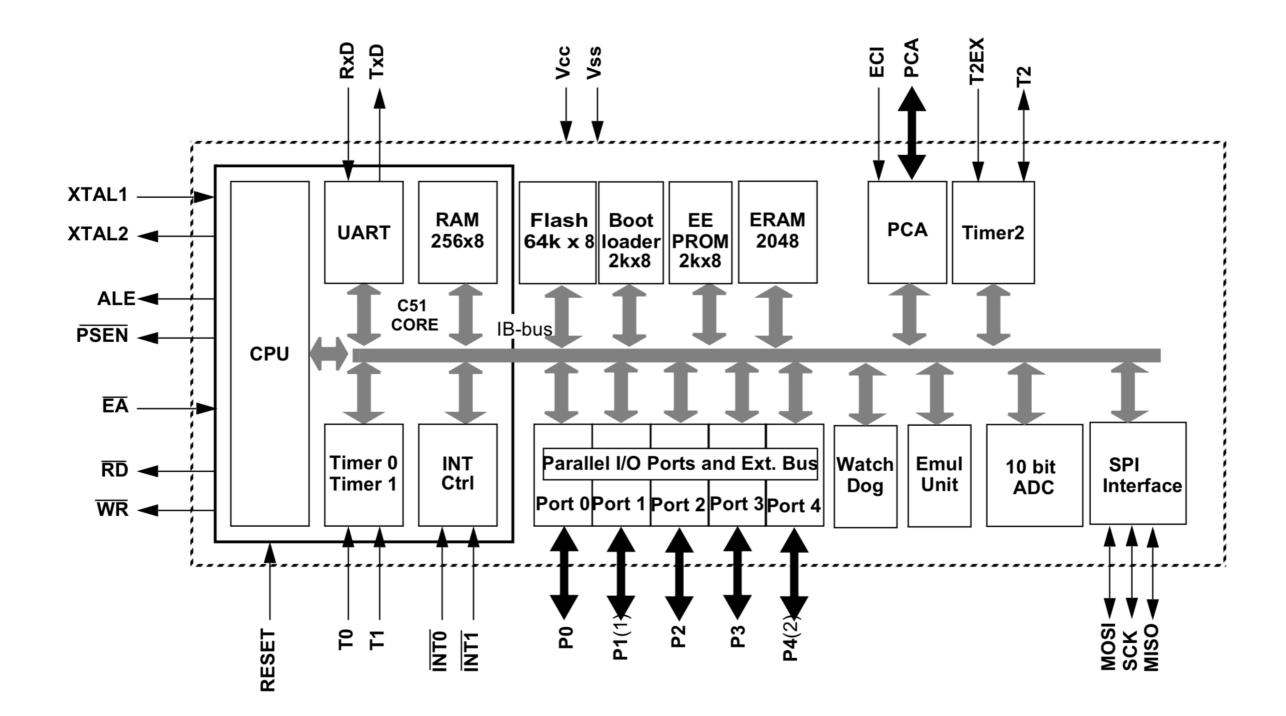

- The 8051 features a watchdog timer.

- The C8051F02x has a 21 bit timer of which 7 bits can be set, allowing custom time-out intervals (of 16 ms to 2 s).

- We won't study this in detail, but keep watchdog timers in mind when building systems that need to automatically recover from unexpected errors.

- For more information on setting up and using the 8051's watchdog timer, see page 129 of C8051F02x.pdf.pdf.

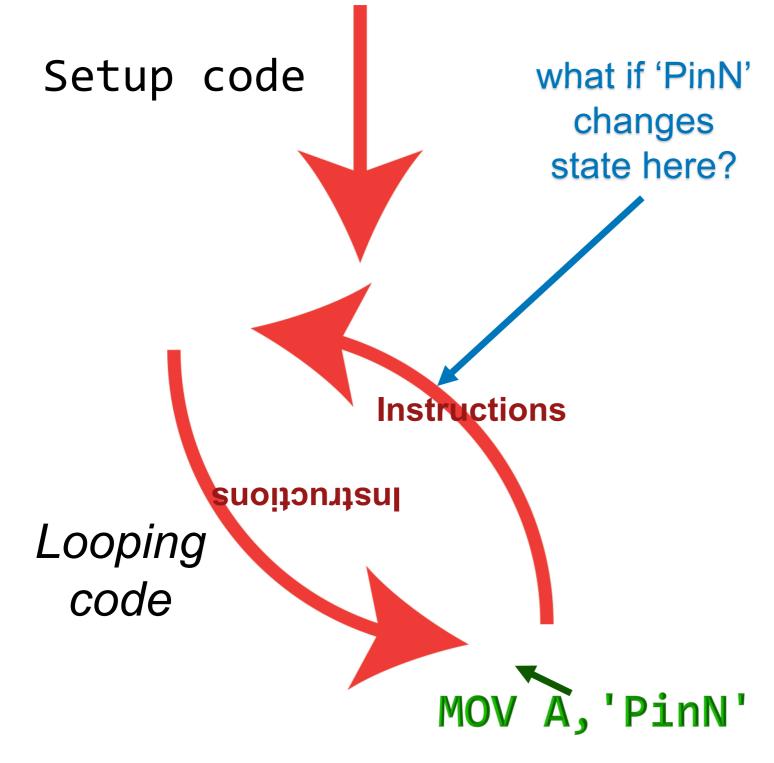

### BLOCKING CODE

What if 'PinN' changes during one of the blocks of instructions? And what if it's *very* important that we not miss 'PinN' changing state? We might solve this by configuring an interrupt to call some code and leave the predefined instructions whenever the pin changes.

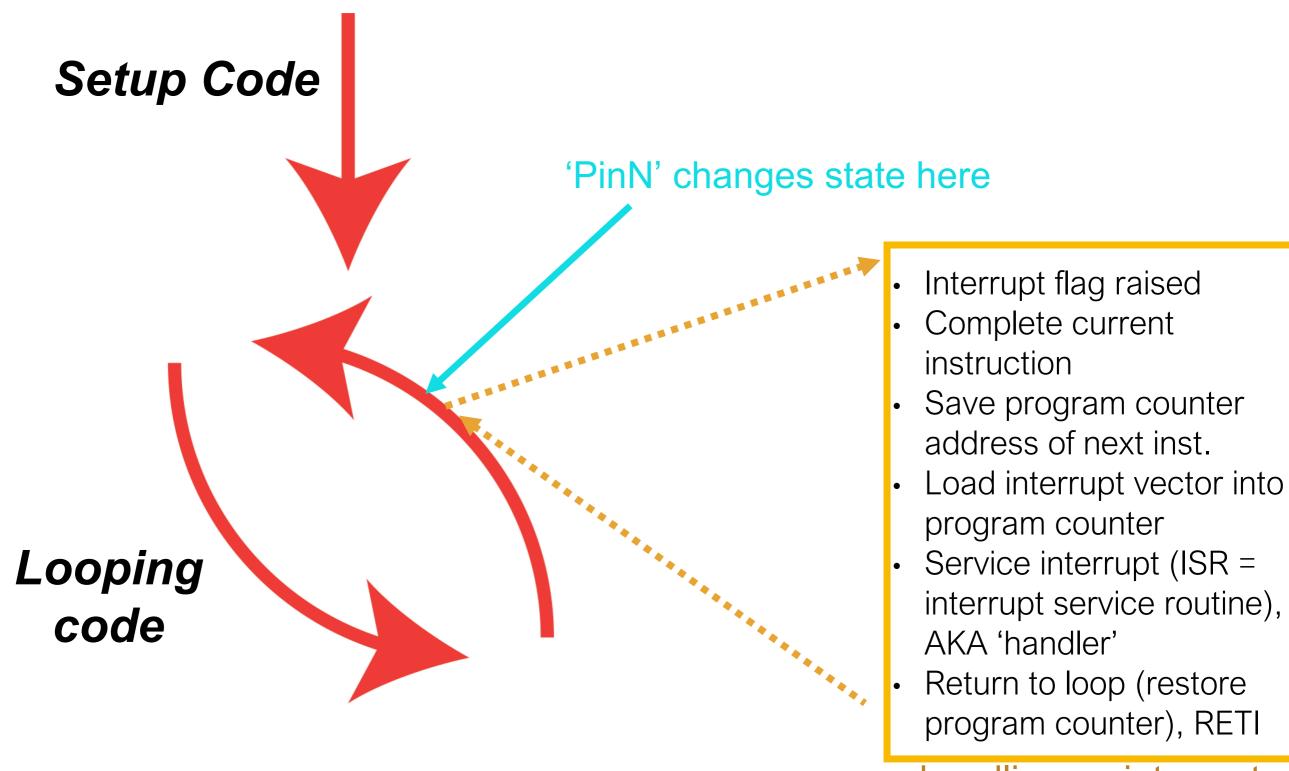

#### INTERRUPT-DRIVEN CODE

handling an interrupt

### Introduction to Interrupts

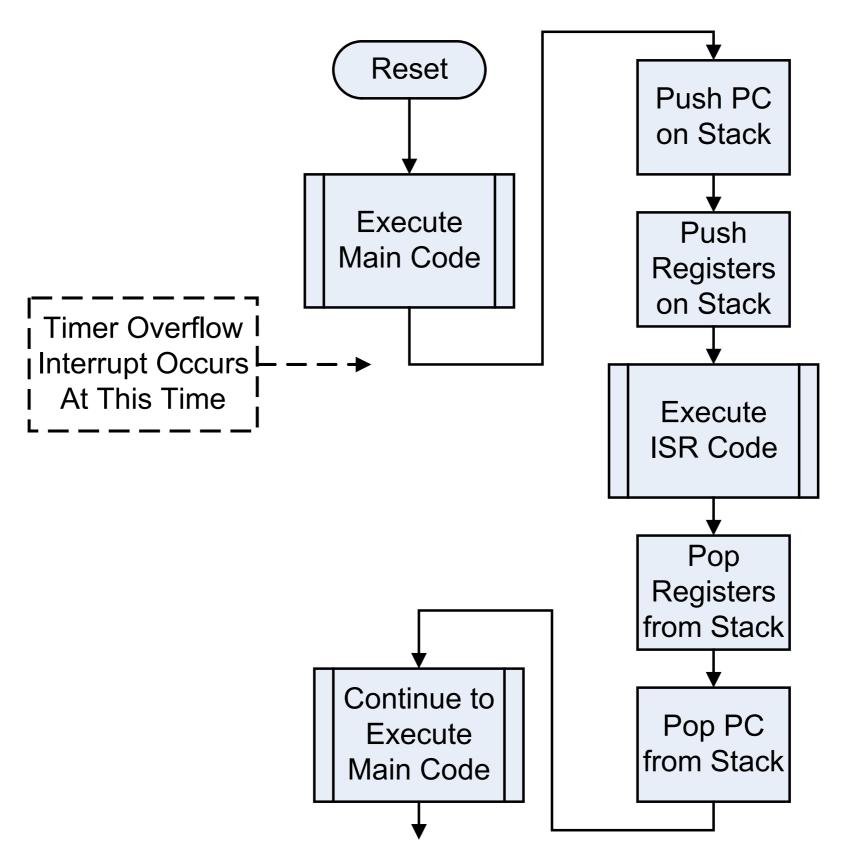

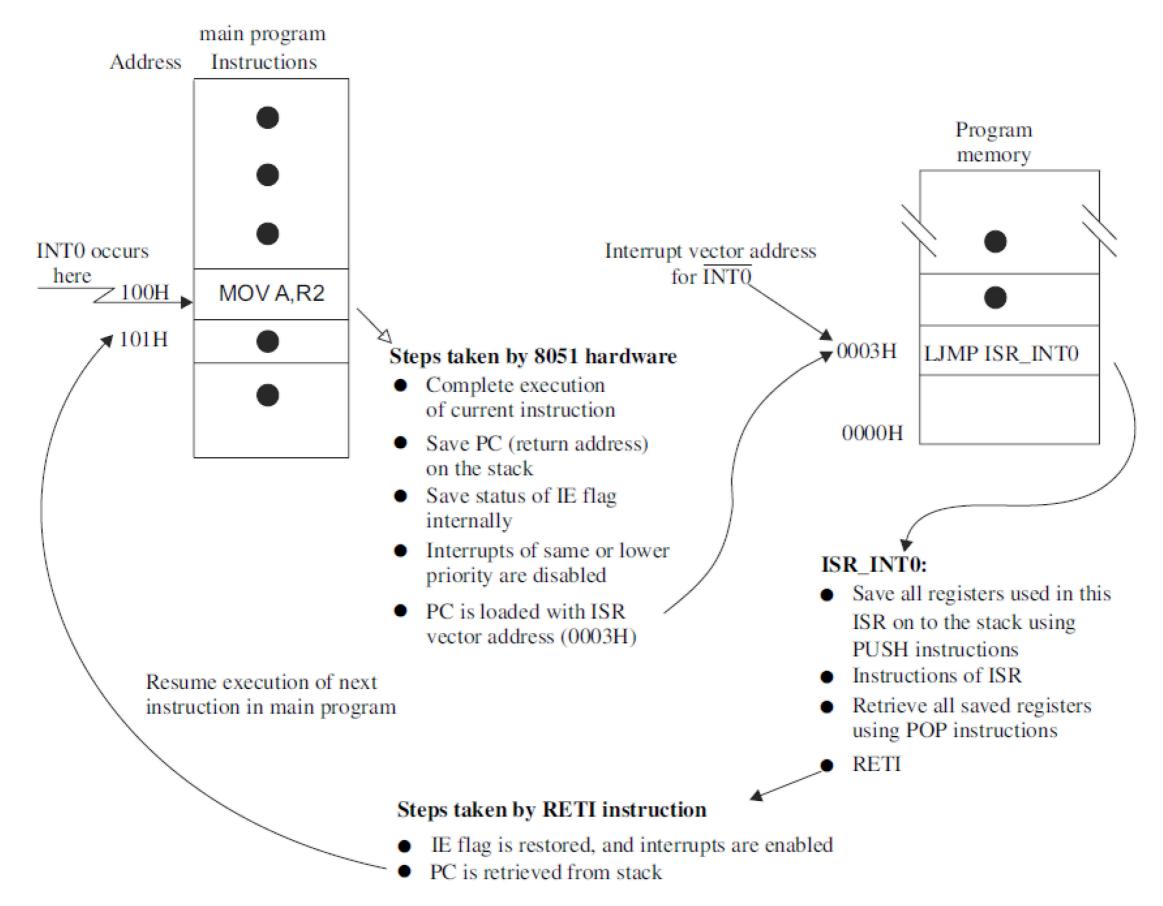

- An interrupt is the occurrence of a condition that causes a temporary suspension of a program while the condition is serviced by another (sub) program

- Interrupts are important because they <u>allow a system to respond</u> <u>asynchronously to an event</u> and deal with the event while in the middle of performing another task

- An interrupt-driven system gives the illusion of doing many things simultaneously

- The (sub) program that deals with an interrupt is called an interrupt service routine (ISR) or interrupt handler

### Introduction

- The ISR executes in response to the interrupt and generally performs an input or output operation to a device

- When an interrupt occurs, the main program temporarily suspends execution and branches to the ISR

- The ISR executes, performs the desired operation, and terminates with a "return from interrupt" (RETI) instruction

- The RETI instruction is different from the normal "RET" instruction

## Interrupt Organization

- The 8051 supports many interrupt sources, including:

- external interrupts

- timer interrupts

- serial port interrupts

- Each interrupt source has one or more associated interrupt-pending flag(s) located in an SFR

- When a peripheral or external source meets a valid interrupt condition, the associated interrupt-pending flag is set to 1

- These interrupt flags are "level sensitive" in that if the flag is not cleared in the ISR by either hardware or software, the interrupt will trigger again, even if the event that originally caused the interrupt did not occur again

- All interrupts are disabled after a system reset and enabled individually by software

- Interrupts allow special routines to be run when the microcontroller enters certain states.

- We'll discuss the 8051-specific states below, but interrupts are often associated with microcontrollers' hardware peripherals:

- When some hardware peripheral (timer, serial port, external I/O port, etc.) changes state, main program flow can be set to be interrupted to handle this change in a timely manner.

- Interrupts disrupt the running of normal code.

- It is important to follow best practices with interrupts to keep from disrupting normally-running code:

- Keep interrupt service routines short.

- Try to avoid calling subroutines within your interrupt service routine.

- Ask what might happen if an interrupt is itself interrupted...

- Interrupts are handled in order of a defined priority.

- Consider interrupt priority: which interrupt is most important?

- If particularly time-sensitive code is used (e.g., bit-banging emulation of a serial port), consider disabling interrupts during this routine.

- Re-enable after this routine is finished.

- The ISR executes in response to the interrupt and generally performs an input or output operation to a device

- When an interrupt occurs, the main program temporarily suspends execution and branches to the ISR

- The ISR executes, performs the desired operation, and terminates with a "return from interrupt" (RETI) instruction

- > The RETI instruction is different from the normal "RET" instruction

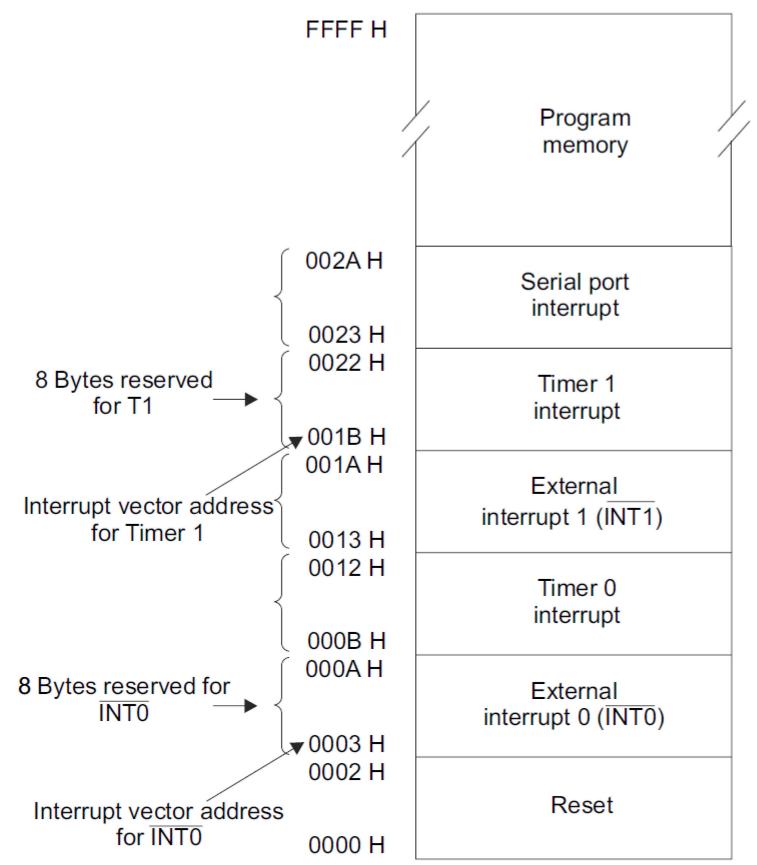

- The original 8051 has four interrupt types.

- RESET: When reset, PC is loaded with ROM address 0x0000

- Unlike other interrupts, prior addresses aren't loaded to stack, etc.

- TIMER INTERRUPTS: one interrupt for Timer 0 and one for Timer 1.

- Timer 0 interrupt: PC is vectored to 0x000B

- Timer 1 interrupt: PC is vectored to 0x001B

- EXTERNAL INTERRUPTS: Interrupts that are called in response to external signals.

- External interrupt 0 INT0 (AKA EXT1): PC vectored to ROM 0x0003.

- External interrupt 1 INT1 (AKA EXT2): PC vectored to ROM 0x0013.

- SERIAL INTERRUPT: Interrupt that is called in response to serial events.

- Serial interrupt: PC is vectored to ROM 0x0023.

- The C8051F020x has additional interrupts; we'll look at these later.

- If the ISR is short, it can fit in the 8 bytes allocated to the interrupts.

- If the ISR is longer, the vector address holds an LJMP instruction that points to another memory location, allowing for a longer ISR.

#### INTERRUPT VECTOR TABLE

| INTERRUPT          | ROM ADDRESS (for start of ISR) | INTERRUPT PIN | NOTES                                                                          |  |

|--------------------|--------------------------------|---------------|--------------------------------------------------------------------------------|--|

| RESET              | 0x0000                         | 9             | Note only 3 bytes of ROM<br>between this and INT0.<br>See example, next slide. |  |

| INTO               | INT0 0x0003                    |               | Interrupt flag auto-<br>clears                                                 |  |

| Timer0             | 0x000B                         | N/A           | Interrupt flag auto-<br>clears                                                 |  |

| INT1 0x0013        |                                | P3.3          | Interrupt flag auto-<br>clears                                                 |  |

| Timer1 0x001B      |                                | N/A           | Interrupt flag auto-<br>clears                                                 |  |

| Serial Port 0x0023 |                                | N/A           | Software must clear this interrupt flag.                                       |  |

#### INTERRUPT VECTOR TABLE

#### INTERRUPT VECTOR TABLE

### RESET

- Note the low ROM addresses for the interrupt vector table addresses.

- Also, note how Reset has only three bytes of ROM (0x0000-0x0002).

- If we're not careful, our PC will just step through the other ISR's and execute them. Instead, we must quickly LJMP past these ISR addresses into an un-used memory space.

- We can use the ORG directive to tell our assembler to assemble the code to make sure that we bypass this vector table.

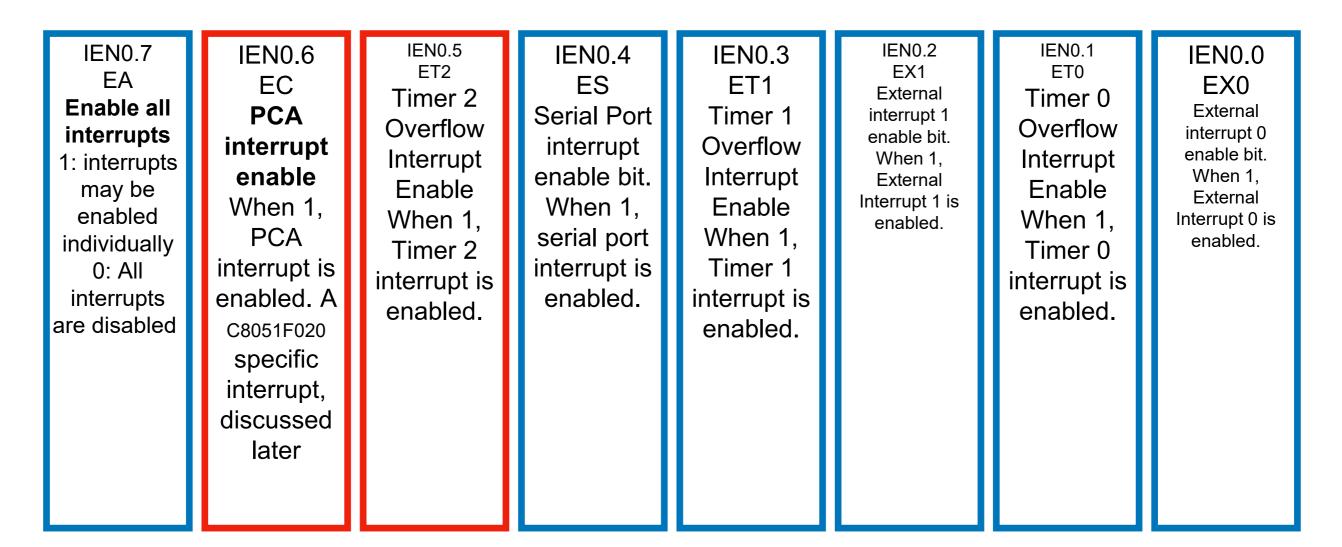

### THE IE (IEN0) REGISTER

- The special function register that allows for interrupt control is the IE register.

- IE = interrupt enable.

- Allows for bit-by-bit control of each individual interrupt as well as all interrupts at once.

- Original 8051's have a single IE register; the C8051F020x has two.

- We'll focus on the first one, called IEN0 on the C8051F020x.

#### Interrupt enable registers

#### IEN0 (S:A8h) Interrupt Enable Register

| 7             | 6               | 5                                                                                                                                  | 4                                                                                                                                                                                                                       | 3   | 2   | 1   | 0   |  |

|---------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-----|--|

| EA            | EC              | ET2                                                                                                                                | ES                                                                                                                                                                                                                      | ET1 | EX1 | ET0 | EX0 |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                        |                                                                                                                                                                                                                         |     |     |     |     |  |

| 7             | EA              | Clear to disa<br>Set to enable<br>If EA=1, eac                                                                                     | Enable All Interrupt bit<br>Clear to disable all interrupts.<br>Set to enable all interrupts.<br>If EA=1, each interrupt source is individually enabled or disabled by setting or<br>clearing its interrupt enable bit. |     |     |     |     |  |

| 6             | EC              | Clear to disa                                                                                                                      | <b>PCA Interrupt Enable</b><br>Clear to disable the PCA interrupt.<br>Set to enable the PCA interrupt.                                                                                                                  |     |     |     |     |  |

| 5             | ET2             | Timer 2 Overflow Interrupt Enable bit<br>Clear to disable Timer 2 overflow interrupt.<br>Set to enable Timer 2 overflow interrupt. |                                                                                                                                                                                                                         |     |     |     |     |  |

| 4             | ES              | Serial Port Enable bit<br>Clear to disable serial port interrupt.<br>Set to enable serial port interrupt.                          |                                                                                                                                                                                                                         |     |     |     |     |  |

| 3             | ET1             | Timer 1 Overflow Interrupt Enable bit<br>Clear to disable timer 1 overflow interrupt.<br>Set to enable timer 1 overflow interrupt. |                                                                                                                                                                                                                         |     |     |     |     |  |

| 2             | EX1             | External Interrupt 1 Enable bit<br>Clear to disable external interrupt 1.<br>Set to enable external interrupt 1.                   |                                                                                                                                                                                                                         |     |     |     |     |  |

| 1             | ET0             | Timer 0 Overflow Interrupt Enable bit<br>Clear to disable timer 0 overflow interrupt.<br>Set to enable timer 0 overflow interrupt. |                                                                                                                                                                                                                         |     |     |     |     |  |

| 0             | EX0             | External Interrupt 0 Enable bit<br>Clear to disable external interrupt 0.<br>Set to enable external interrupt 0.                   |                                                                                                                                                                                                                         |     |     |     |     |  |

Reset Value = 0000 0000b bit addressable

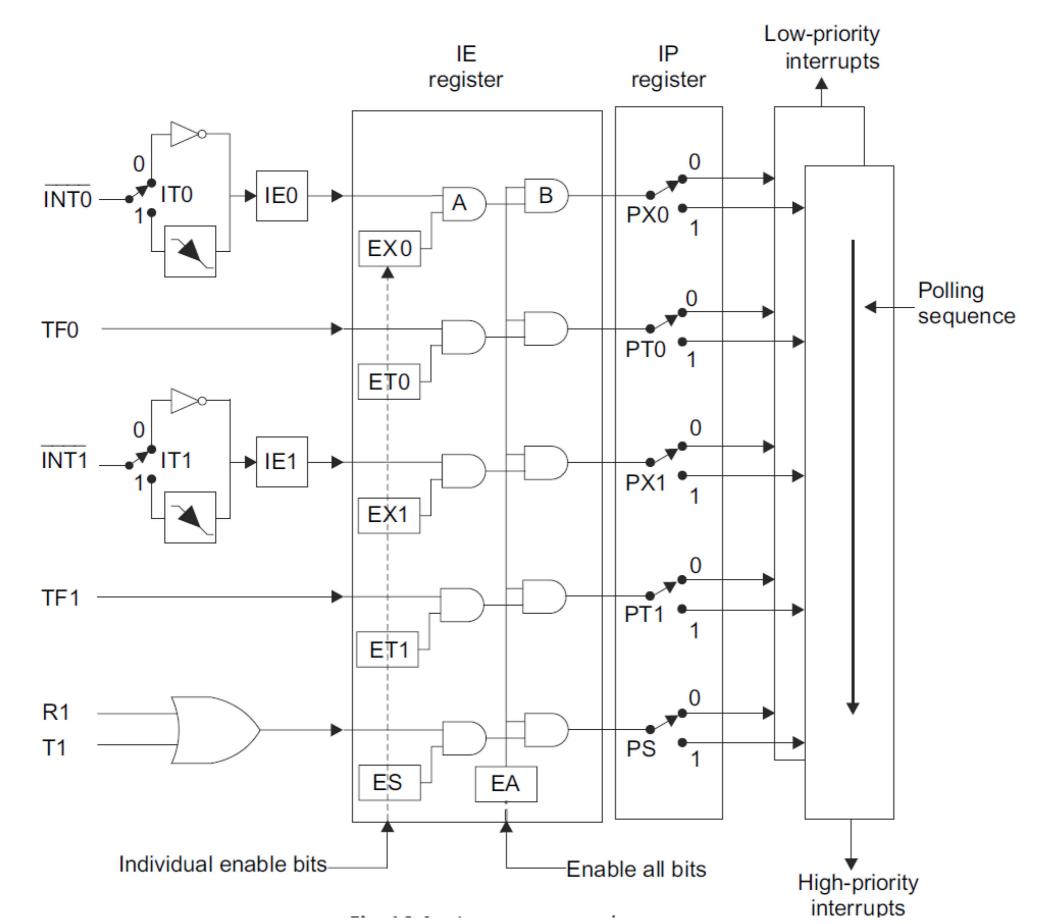

## INTERRUPT PRIORITY

- If we're implementing an interrupt-rich application, we need to consider what happens if multiple interrupts arrive at the same time (interrupt during ISR).

- Older 8051's had less flexible interrupt priority control.

- For more on original 8051 priority, see <u>https://what-when-how.com/8051-</u> microcontroller/interrupt-priority-in-the-805152/

- The C8051F020x has a much more modern interrupt priority configuration capability, which we'll focus upon.

- Upon boot-up, the interrupts are given default priority hierarchy.

- We can change this priority hierarchy by manipulating two SFR's.

- IPL0 and IPH0 registers.

- By default, the interrupt priority is:

- 1. External interrupt 0 (INT0)

- 2. Timer 0 (TF0)

- 3. External interrupt 1 (INT1)

- 4. Timer 1 (TF1)

- 5. Programmable counter array (discussed later) (CF)

- 6. Serial UART (RI or TI)

- 7. Timer 2 (TF2)

- 8. ADC (discussed later) (ADCI)

- 9. SPI (discussed later)

DECREASING PRIORITY

### SETTING INTERRUPT PRIORITY

- Each interrupt has two bits that can set its priority.

- These bits are in the IPH0 and IPL0 registers.

- These two bits give four possible levels of interrupt priority.

- If two interrupts are configured with the same priority level, then they are handled in order of their ranking in the default priority level scheme (prev. slide).

| IPH.x | IPL.x | Priority level (0: lowest, 3:<br>highest) |

|-------|-------|-------------------------------------------|

| 0     | 0     | 0                                         |

| 0     | 1     | 1                                         |

| 1     | 0     | 2                                         |

| 1     | 1     | 3                                         |

#### THE IPL AND IPH REGISTERS

| IPH0                 | IPL0                |       |       |                                              |

|----------------------|---------------------|-------|-------|----------------------------------------------|

| 7. (Reserved)        | 7. (Reserved)       |       |       |                                              |

| 6. PPCH (PCA Int)    | 6. PPC (PCA Int)    | IPH.x | IPL.x | Priority level<br>(0: lowest, 3:<br>highest) |

| 5. PT2H (Timer2)     | 5. PT2 (Timer2)     | 0     | 0     | 0                                            |

| 4. PSH (Serial port) | 4. PS (Serial port) | 0     | 1     | 1                                            |

| 3. PT1H (Timer 1)    | 3. PT1 (Timer 1)    |       | 0     | 0                                            |

| 2. PX1H (INT1)       | 2. PX1 (INT1)       | 1     | 0     | 2                                            |

| 1. PT0H (Timer 0)    | 1. PT0 (Timer 0)    | 1     | 1     | 3                                            |

| 0. PX0H (INT0)       | 0. PX0 (INT0)       |       |       |                                              |

#### Interrupt control structure

### TIMER INTERRUPTS

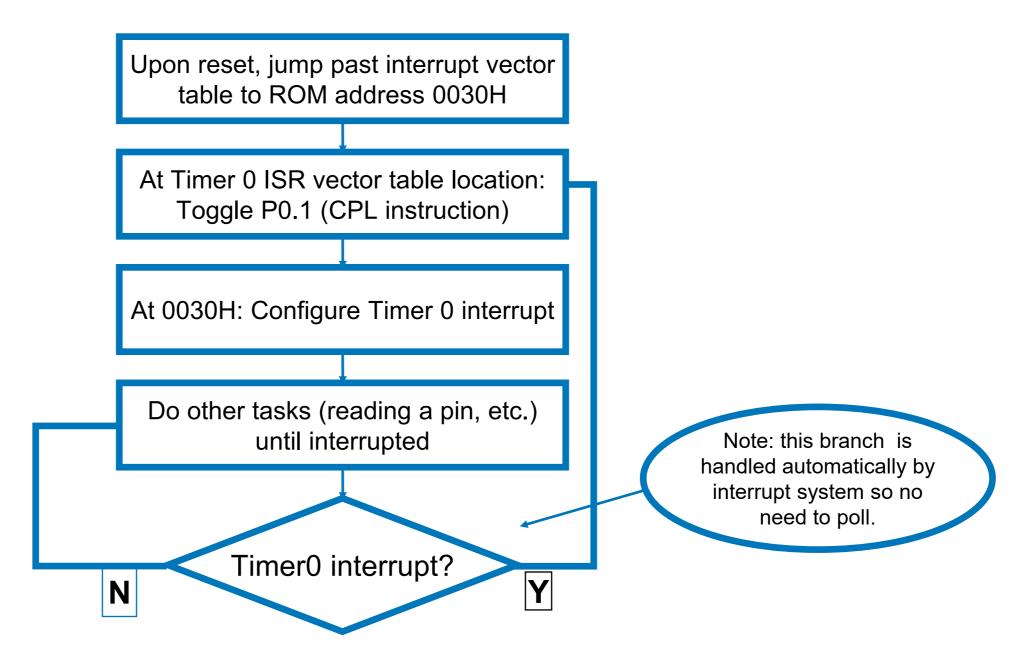

- Goal: replicate the "EXAMPLE SQUARE WAVE" code from a previous slide, replacing polling approach with an interrupt-driven approach.

- Advantages: we can free up the CPU from having to monitor the TFx flag.

- For this example, we'll keep the ISR short so it will fit within the 8 Bytes of ROM allocated by the Interrupt Vector Table.

#### TIMER INTERRUPT EXAMPLE

;We'll be using the interrupt address space, so we need to make ; sure that our main program bypasses this. **ORG 0000H** ;Jump past the interrupt vector table. LJMP MAIN ;--ISR for Timer 0. Will generate a square wave at Port 0.1 ORG 000BH ;Assembler will place code at Timer0 vector adr. CPL P0.1 ;Toggle Port 0 pin 1 MOV TL0,#00 ;Must reload timer values manually in this mode MOV TLH, #80H ;Return from int.; pops PC and resets interrupt logic RETI ;-- Main body of program. Start by configuring Timer 0 ;Directs assembler past interrupt vector table ORG 0030H MAIN: MOV TMOD, #0000001B ; Timer 0, mode 1 MOV TL0, #00 ; Initially load timer values MOV TLH, #80H MOV IEN0, #10000010B ;Enable timer 0 interrupt SETB TRO ;Start the timer IDLE: SJMP IDLE ;Loop here until interrupt. No polling of int flag! **END**

### EXTERNAL INTERRUPTS

- In addition to interrupting normal program flow in response to a timer, external pin activations can be set to interrupt program flow.

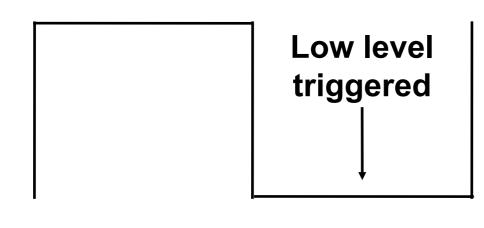

- On the 8051, interrupts can be set to be triggered in response to two different types of pin states/state changes:

- Low level triggered: when the external interrupt pin is LOW, the interrupt is triggered.

- The interrupt will be re-triggered if the pin remains low after the ISR!

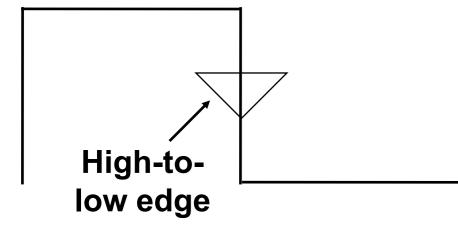

- Edge triggered interrupt: interrupt is triggered on falling edge of signal at external interrupt pin.

- Falling edge: when pin goes from HIGH to LOW.

- Low-level or falling edge mode: configured in TCON register.

- Need to trigger on rising edge? Use an inverter chip (e.g., 7404)

### EXTERNAL INTERRUPT CONFIGURATION

- Low 4 bits of TCON register: configure/examine external interrupts.

- TCON.3 (IE1) and TCON.1 (IE0): 'external interrupt occurred' flags.

- TCON.2 (IT1) and TCON.0 (IT0): set interrupt trigger type.

| TCON.7<br>TF1<br>Timer 1<br>Overflow<br>Flag<br>1 when<br>overflow<br>occurs.<br>Must be<br>cleared in<br>software;<br>auto.<br>cleared<br>when<br>leaving ISR | TCON.6<br>TR1<br>Timer 1 run<br>bit<br>1: Start<br>timer<br>0: Stop<br>timer<br>(Software<br>controlled) | TCON.5<br>TF0<br>Timer 0<br>Overflow<br>Flag<br>1 when<br>overflow<br>occurs.<br>Must be<br>cleared in<br>software;<br>auto.<br>cleared<br>when<br>leaving ISR | TCON.4<br>TR0<br>Timer 0 run<br>bit<br>1: Start<br>timer<br>0: Stop<br>timer<br>(Software<br>controlled | TCON.3<br>IE1<br>Ext.<br>interrupt1<br>edge flag.<br>1: external<br>interrupt<br>occurred.<br>0: External<br>interrupt<br>processed.<br>(Hardware<br>controlled;<br>no need to<br>edit this) | TCON.2<br>IT1<br>Interrupt1<br>trigger type<br>select bit.<br>1: Interrupt<br>occurs on the<br>falling edge of<br>INT1.<br>0: Interrupt<br>occurs on<br>INT1's level<br>being LOW. | TCON.1<br>IE0<br>Ext.<br>interrupt0<br>edge flag.<br>1: external<br>interrupt<br>occurred.<br>0: External<br>interrupt<br>processed.<br>(Hardware<br>controlled;<br>no need to<br>edit this) | TCON.0<br>ITO<br>Interrupt0<br>trigger type<br>select bit.<br>1: Interrupt<br>occurs on the<br>falling edge of<br>INT1.<br>0: Interrupt<br>occurs on<br>INT1's level<br>being LOW. |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

### EXTERNAL INTERRUPT EXAMPLE

- Goal: Toggle an LED connected to Port 1, pin 3.

- This LED will be toggled when an external interrupt (INT1) arrives.

| ORG 0000H     |                                                      |  |  |  |  |  |

|---------------|------------------------------------------------------|--|--|--|--|--|

| LJMP MAIN     | ;Jump past the interrupt vector table.               |  |  |  |  |  |

|               |                                                      |  |  |  |  |  |

| ;- ISR: Inter | rupt 1, toggles LED when new interrupt arrives.      |  |  |  |  |  |

| ORG 0013H     | ;Location in vector table of INT1                    |  |  |  |  |  |

| CPL P1.3      | ;Toggle Port 1 pin 3                                 |  |  |  |  |  |

| RETI          | ;Reset PC and clear interrupt flags                  |  |  |  |  |  |

|               |                                                      |  |  |  |  |  |

| ;Set up inter | ;Set up interrupts at ROM location past vector table |  |  |  |  |  |

| ORG 0030H     |                                                      |  |  |  |  |  |

| MAIN: SETB TC | ON.2 ;Interrupt is falling edge triggered            |  |  |  |  |  |

| MOV IENO #100 | 00100B ;Enable interrupts, INT1                      |  |  |  |  |  |

|               |                                                      |  |  |  |  |  |

| IDLE: SJMP ID | LE ;Other code could go here. Idle main CPU for now. |  |  |  |  |  |

| END           |                                                      |  |  |  |  |  |

|               |                                                      |  |  |  |  |  |