#### XMUT 202 Digital Electronics

A/Prof. Pawel Dmochowski

School of Engineering and Computer Science Victoria University of Wellington

CAPITAL CITY UNIVERSITY

The 555 timer is a very useful IC as it can be configured as either a monostable or astable multivibrator.

•Basic design ~1971. Now available in CMOS and in 2-in-1 version (556)

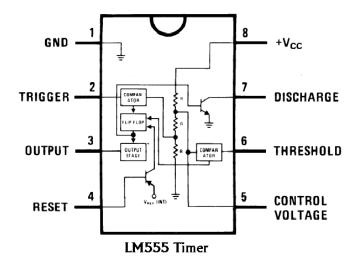

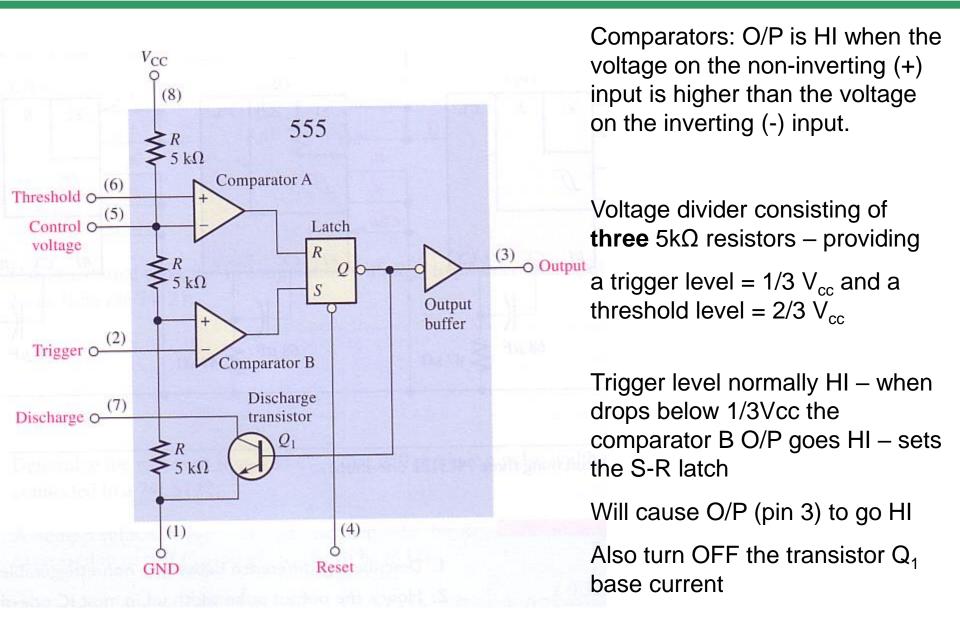

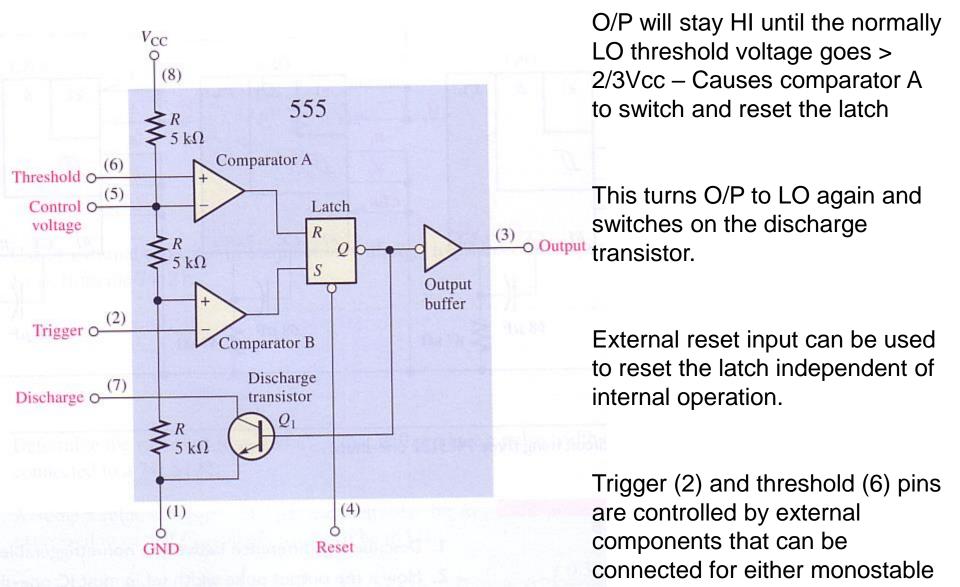

• Use 2 internal comparators: O/P is HI when the voltage on the non-inverting (+) input is higher than the voltage on the inverting (-) input.

#### Internal construction of a 555 Timer

#### Internal construction of a 555 Timer

or astable operation.

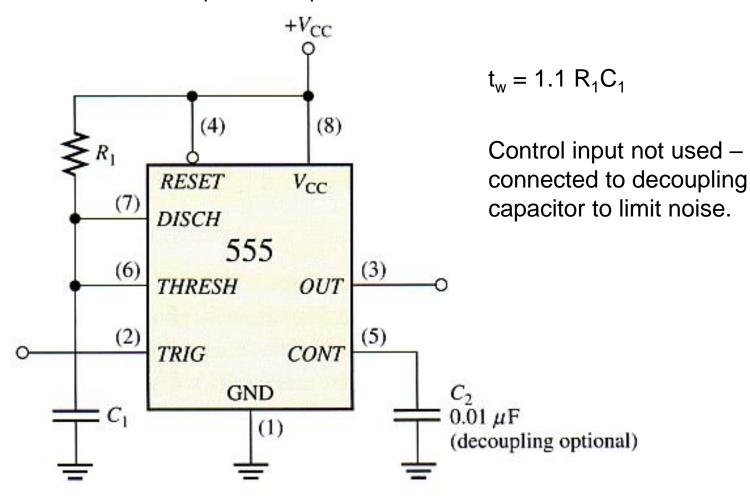

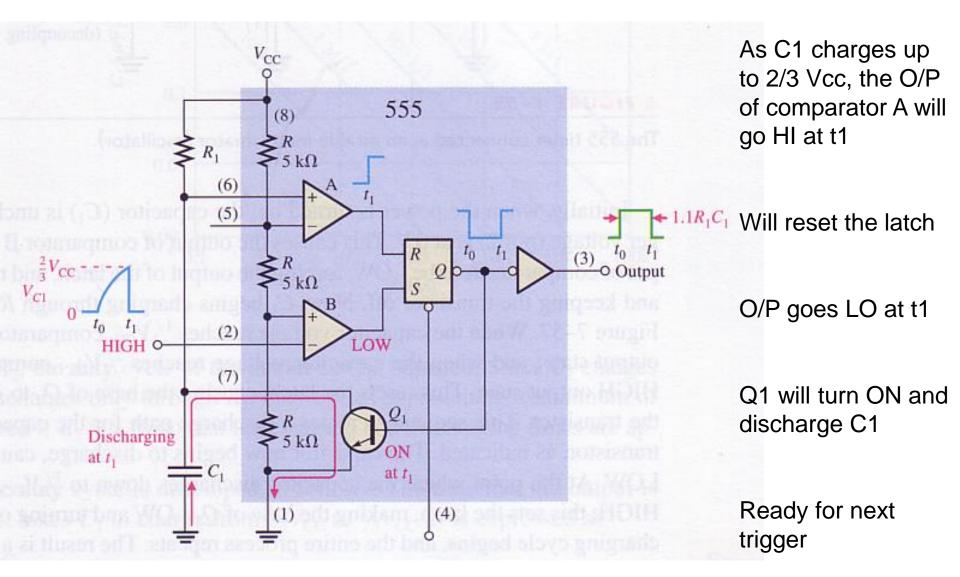

#### 555 Timer connected as a one-shot (monostable)

External  $R_1$  and  $C_1$  connected as shown below.

.

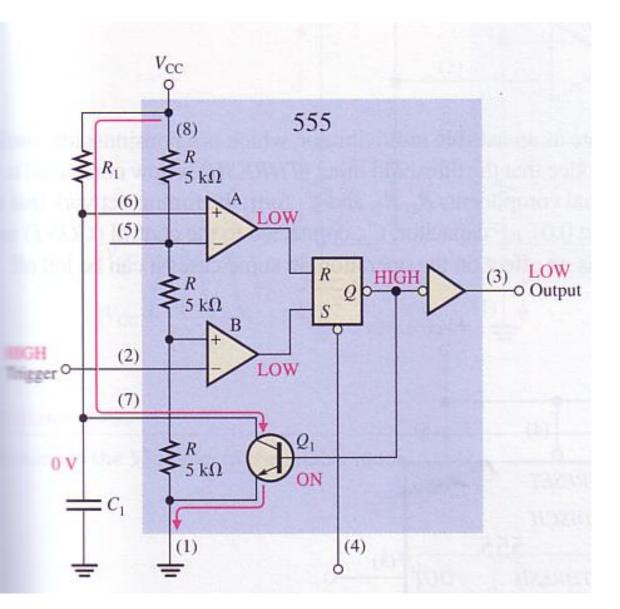

#### Prior to triggering

O/P is LO and Q1 is ON – keeps C1 discharged.

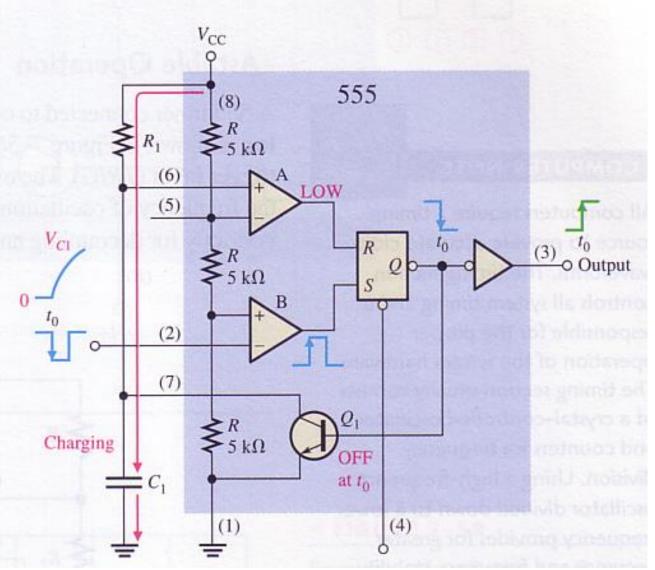

#### When triggered

NG trigger pulse is applied – Comparator B switches to HI and the O/P switches to HI

Q1 turns off

Capacitor C1 starts to charge through R1

#### At end of charging interval

#### **Astable Multivibrators = Clocks**

<u>Astable</u> or <u>free-running multivibrators</u> switch back and forth between two unstable states. This makes it useful for generating clock signals for synchronous circuits.

Different applications place varying demand on clock circuits in terms of precision and long term stability

- Low end Digital IC based clocks

- Medium Crystal oscillator circuits

- Temperature controlled crystal oscillators, atomic clocks

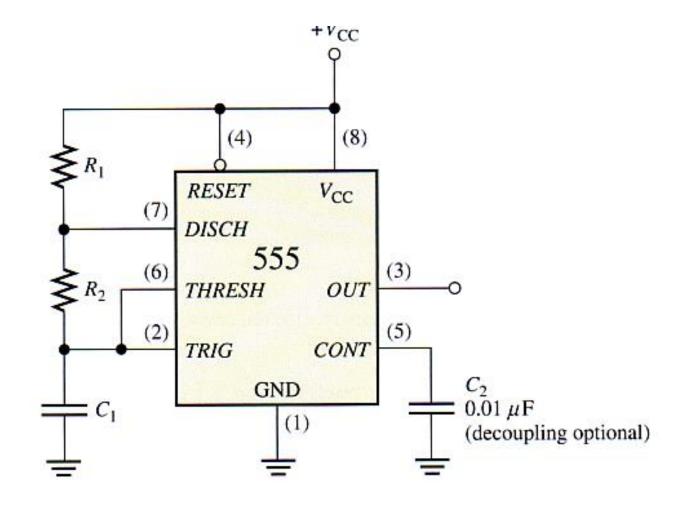

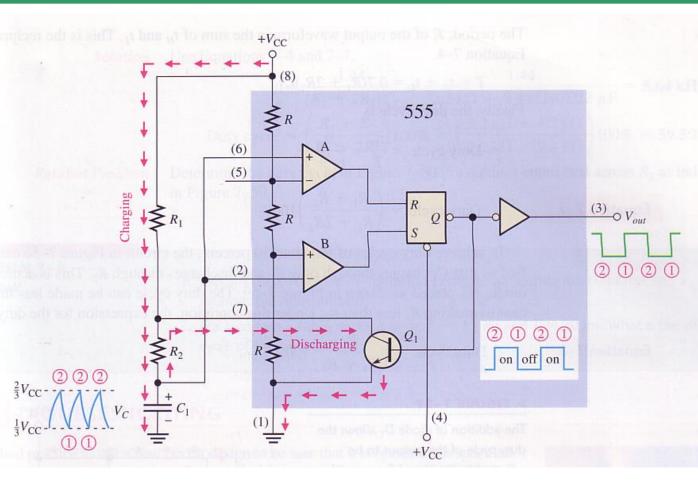

#### The 555 connected as an astable (free running) multivibrator

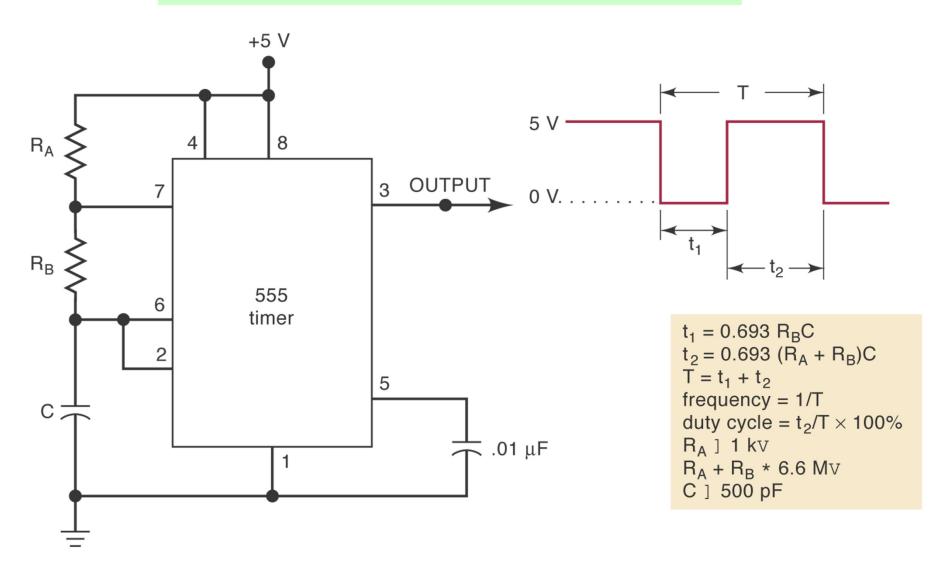

#### The 555 Timer as an Astable Multivibrator.

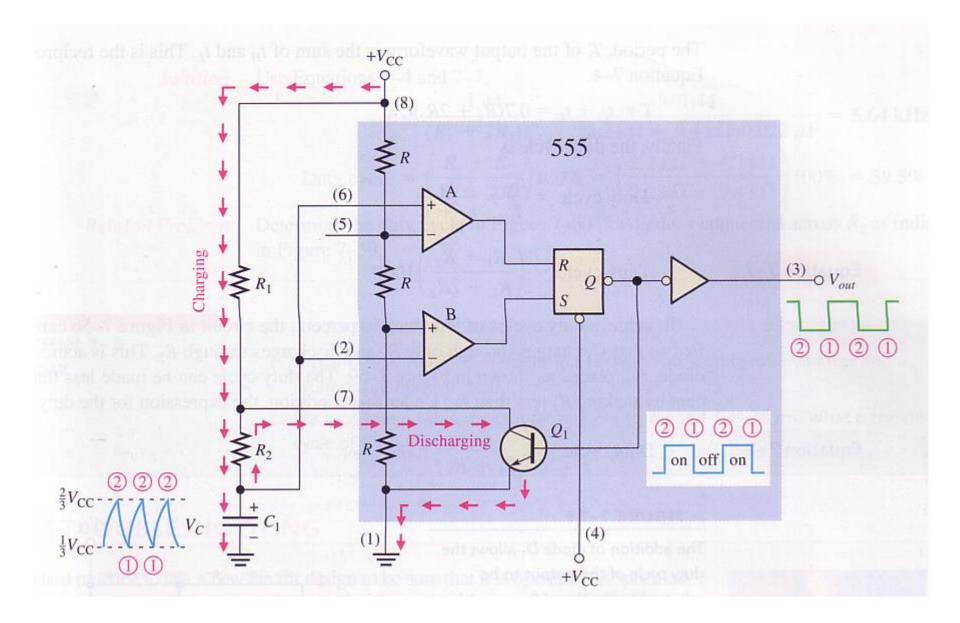

#### Astable operation

Threshold (6) now connected to the trigger (2) input

Two external resistors and a capacitor

2<sup>nd</sup> Capacitor (on Control) for decoupling only – can be left off

Initially capacitor is uncharged – trigger pin (2) is at 0V

This causes O/P of Comp B = HI and Comp A = LO This will keep Q1 OFF

Capacitor will now start to charge through R1 and R2

When it reaches 1/3 Vcc Comp B will switch to LO, when it reached 2/3 Vcc Comp A will switch to HI – Will now reset the latch.

This switches on Q1 and discharges capacitor through R2.

When capacitor discharges to 1/3Vcc Comp B goes HI and sets the latch again.

This turns off Q1 – Another charge cycle of the capacitor starts

Calculate the frequency and the duty cycle of the 555 astable multivibrator output for  $C = 0.001 \ \mu\text{F}$ ,  $R_A = 2.2 \text{ k}\Omega$ , and  $R_B = 100 \text{ k}\Omega$ .

Design a 555 free-running oscillator to produce an approximate square wave at 40 kHz. *C* should be kept at 500 pF or greater.

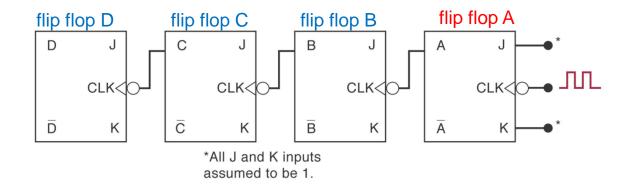

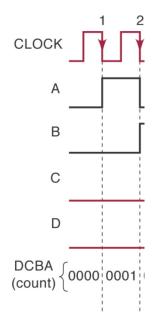

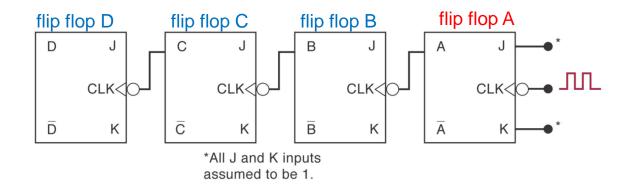

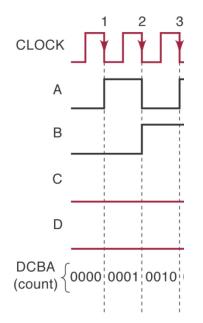

#### Synchronous vs Asynchronous Counters

- Combining flip-flops and logic gates to form various counters and registers.

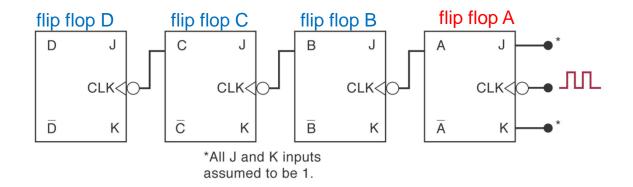

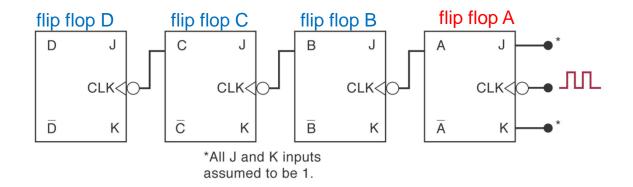

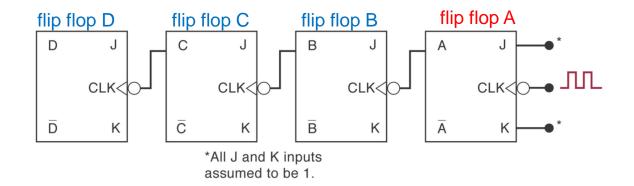

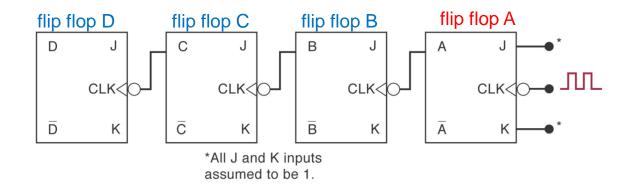

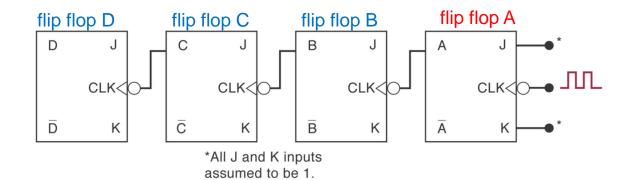

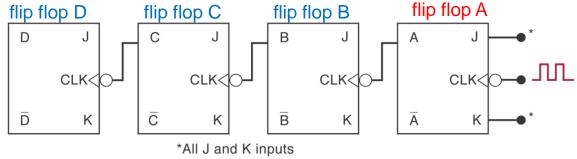

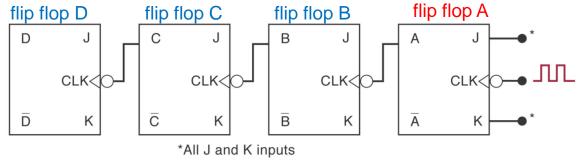

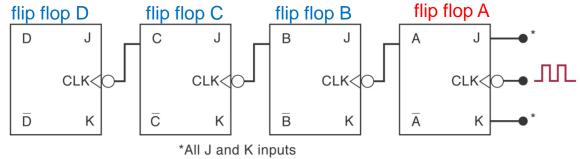

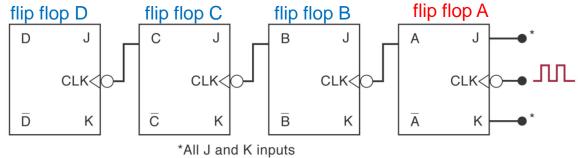

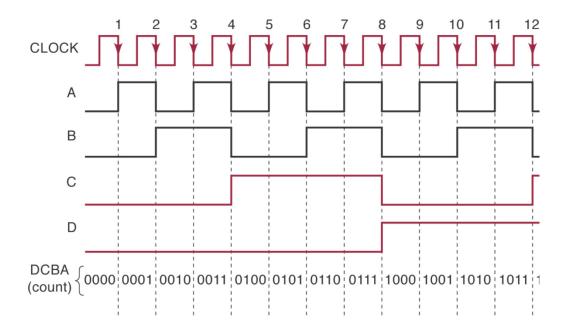

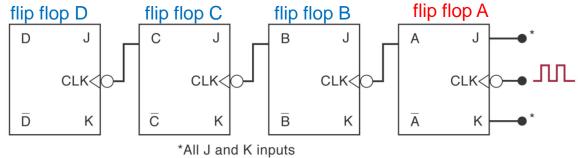

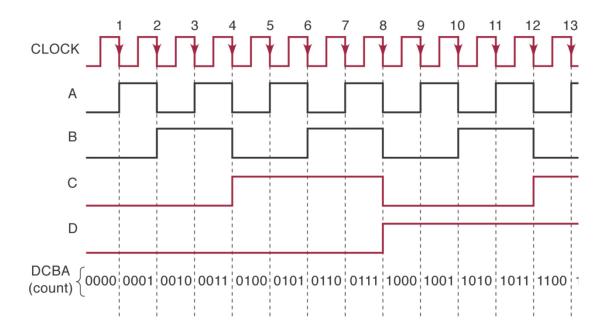

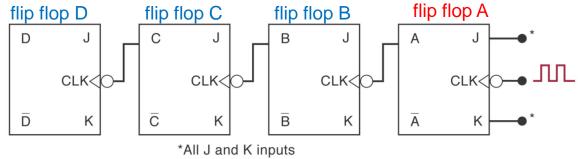

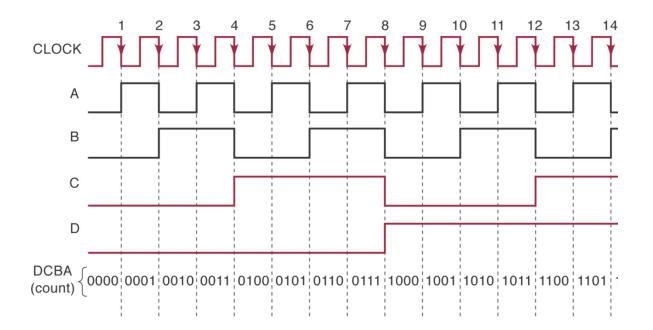

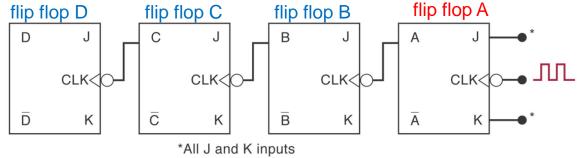

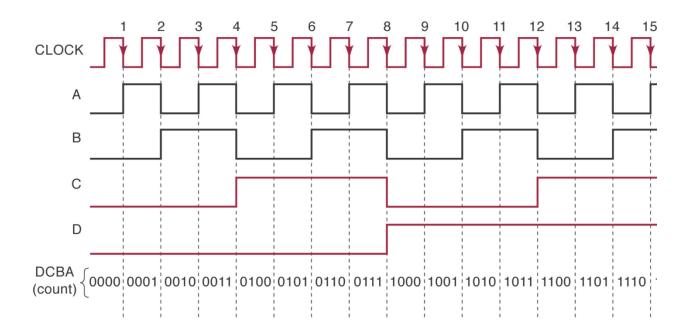

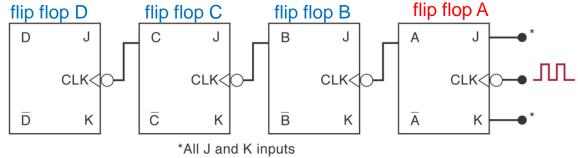

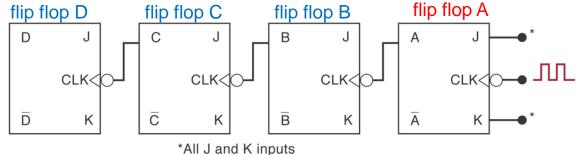

- Asynchronous (Ripple) Counters

- Synchronous (Parallel) Counters

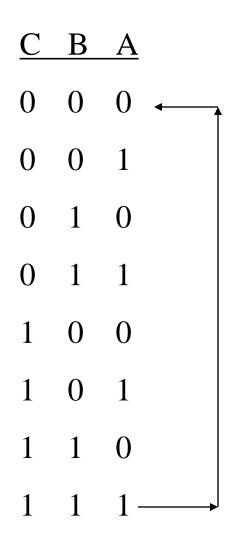

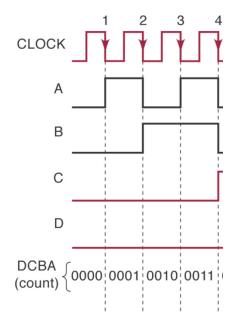

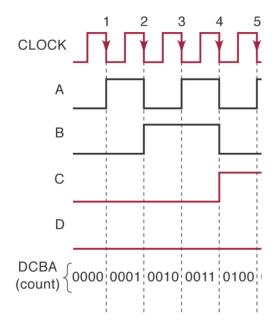

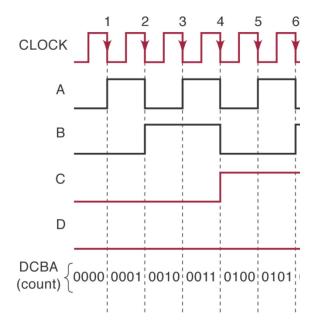

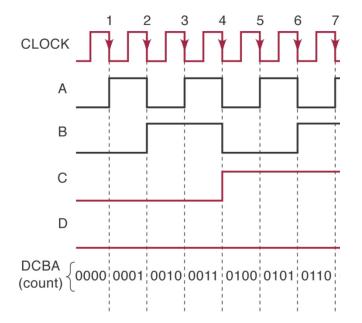

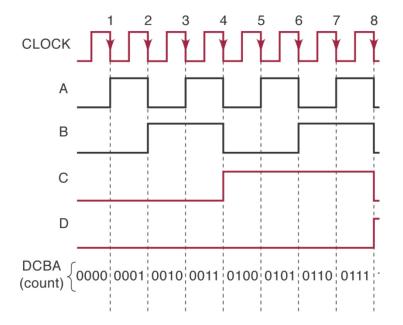

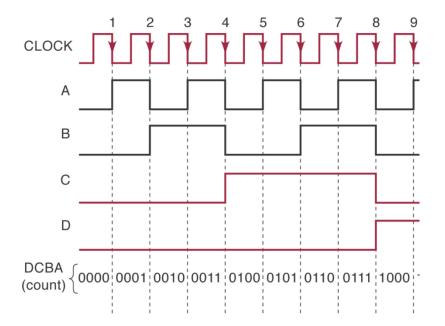

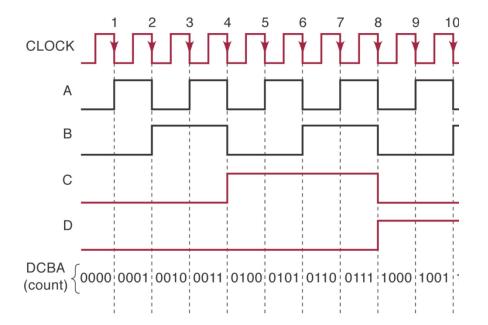

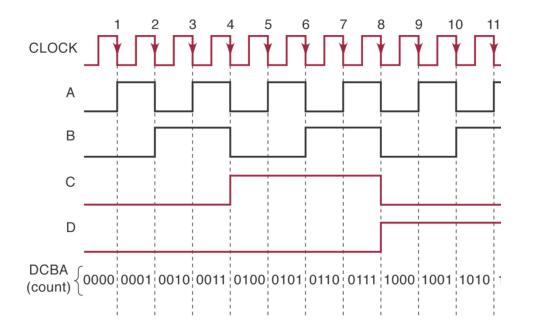

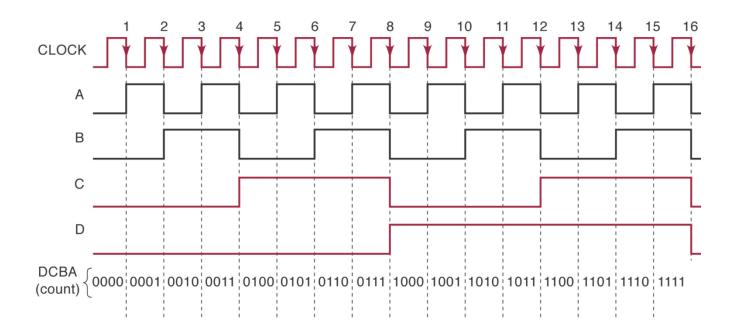

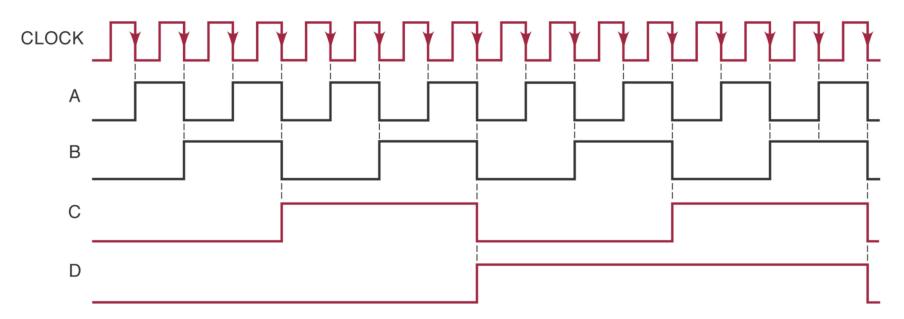

A: Toggles as normal (every step)B: Toggles when A goes HI to LOC: Toggles when B goes HI to LO

Counters that are made of flip flops that are supplied with different clock signals.

Counters that are made of flip flops that are supplied with different clock signals.

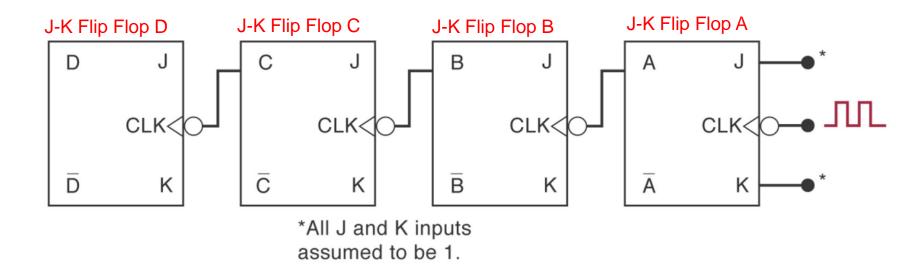

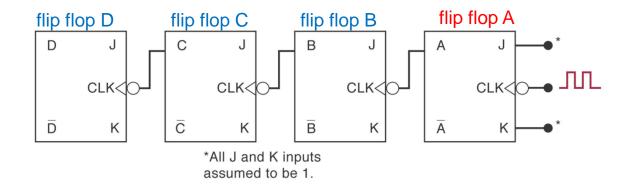

- Review of four bit counter operation

- Clock is applied only to flip flop A. J and K are high in all flip flops.

- Output of flip flop A is CLK of flip flop B and so forth.

- Flip flop outputs D, C, B, and A are a 4 bit binary number with D as the MSB.

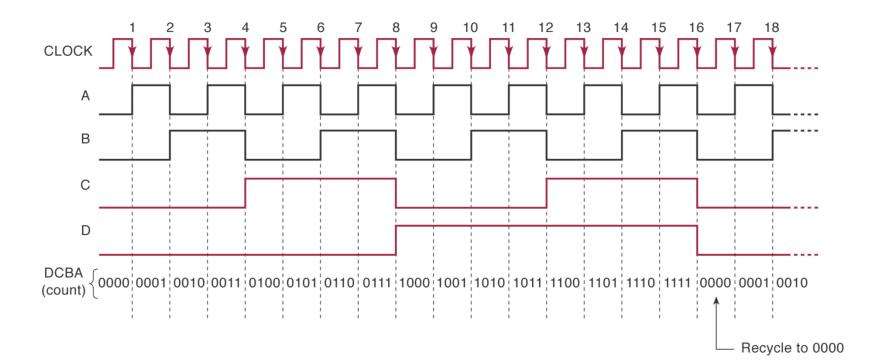

- After the NGT of the 16<sup>th</sup> clock pulse the counter recycles to 0000.

- This is an <u>asynchronous counter</u> because state is not changed in exact synchronism with the clock.

MOD number is equal to the number of states that the counter goes through before recycling. Adding flip flops will increase the MOD number.

- MOD number is equal to the number of states that the counter goes through before recycling. Adding flip flops will increase the MOD number.

- MOD number =  $2^n$ , where n = number of flip-flops.

- MOD number is equal to the number of states that the counter goes through before recycling. Adding flip flops will increase the MOD number.

- MOD number =  $2^n$ , where n = number of flip-flops.

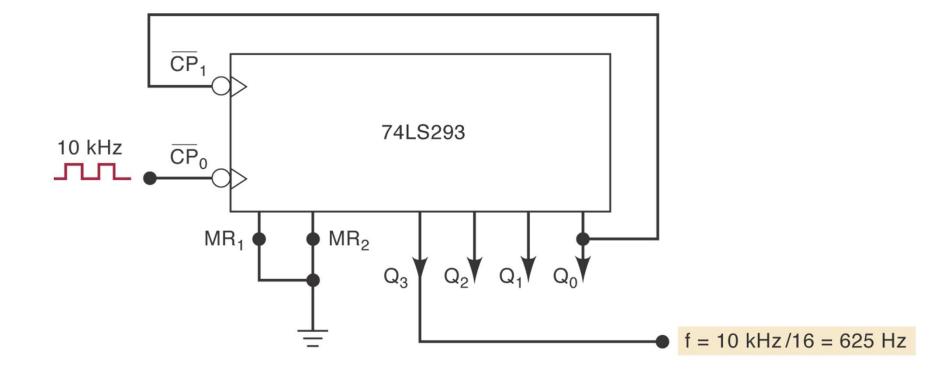

- The output of the last flip flop (MSB) divides the input clock frequency by the MOD number.

### **Frequency Division**

Each flip flop will have an output frequency of <sup>1</sup>/<sub>2</sub> the input.

- Each flip flop will have an output frequency of <sup>1</sup>/<sub>2</sub> the input.

- The output frequency of the last flip flop of any counter will be the clock frequency divided by the MOD of the counter.

- Each flip flop will have an output frequency of <sup>1</sup>/<sub>2</sub> the input.

- The output frequency of the last flip flop of any counter will be the clock frequency divided by the MOD of the counter.

**Timing Diagram**

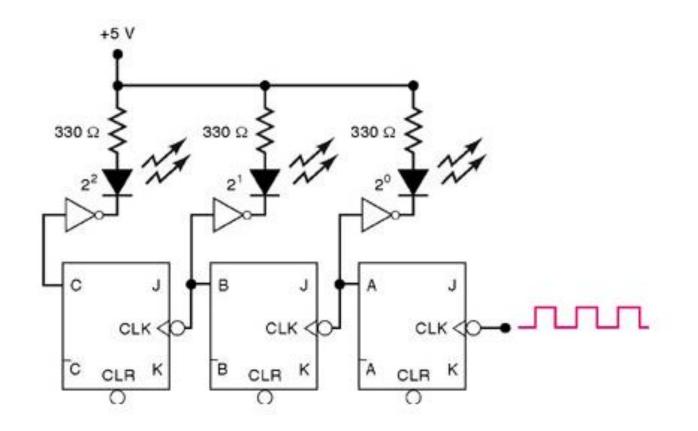

The arrangement below will result in an LED on when the output is high.

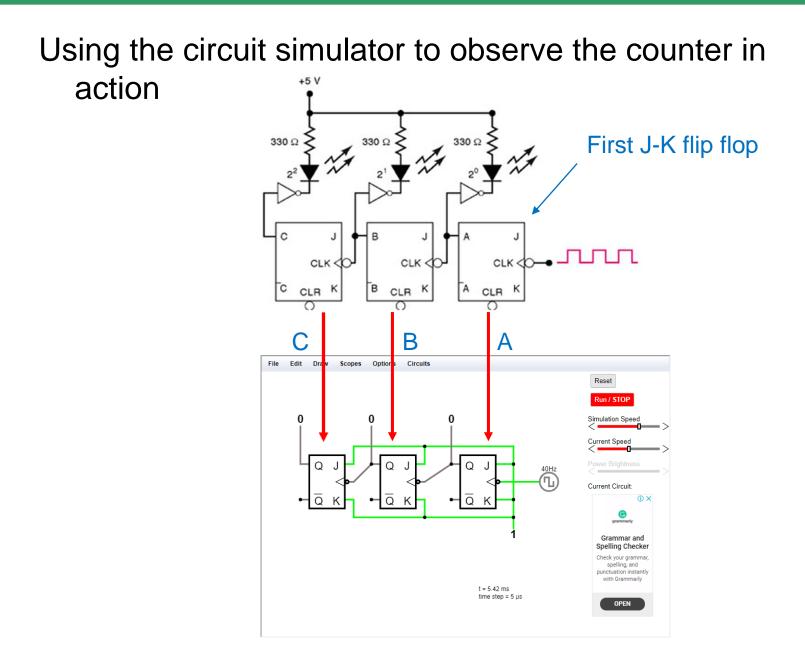

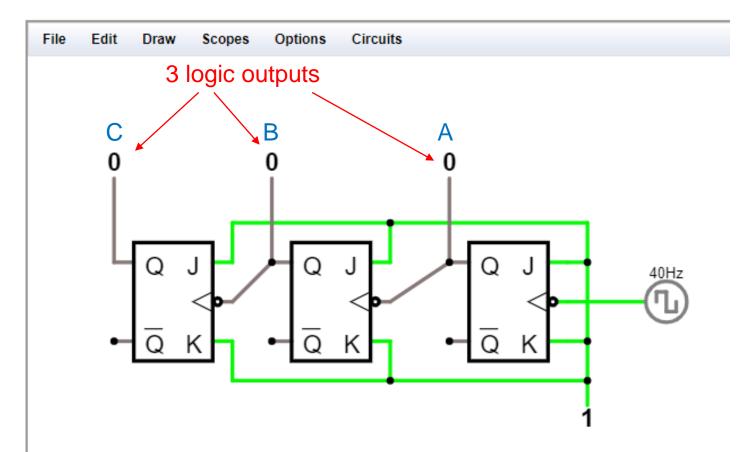

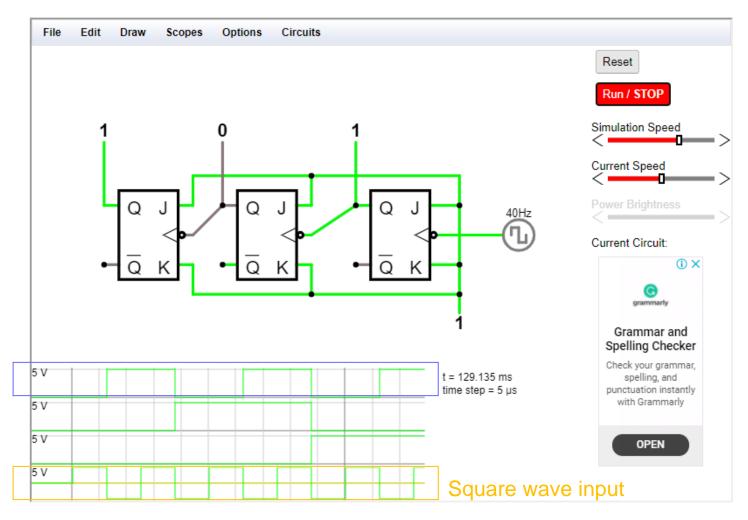

# Using the circuit simulator to observe the counter in action

# Using the circuit simulator to observe the counter in action

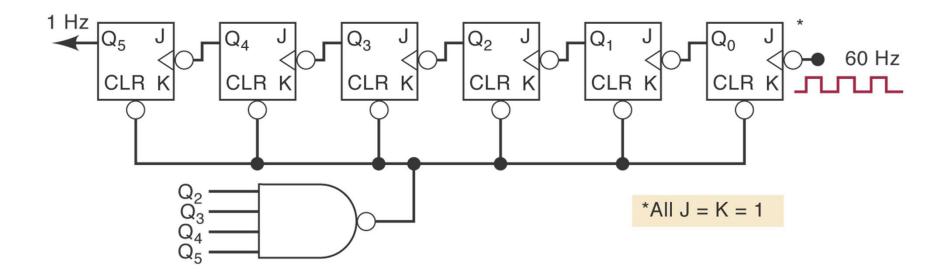

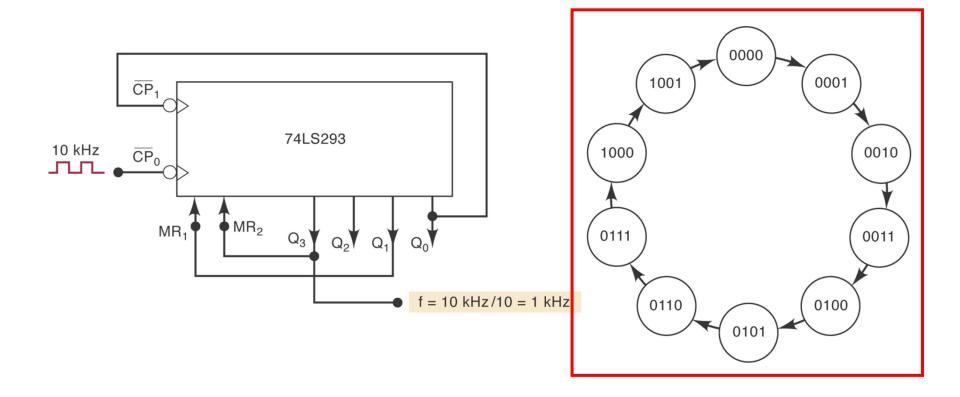

## **Counters with MOD Number** <2<sup>*N*</sup>

The MOD of a counter can be changed by designing the counter to reset on a specific counter state.

## **Counters with MOD Number < 2**<sup>*N*</sup>

The MOD of a counter can be changed by designing the counter to reset on a specific counter state.

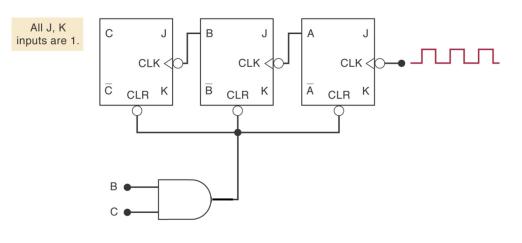

Turns MOD 8 counter into a MOD 6 counter

## **Counters with MOD Number** <2<sup>*N*</sup>

The MOD of a counter can be changed by designing the counter to reset on a specific counter state.

All J, K С J В J J А inputs are 1. CLK < CLK < CLK <  $\overline{\mathsf{C}}$ Ā CLR K В CLR K CLR K B 🖝 Input 3 5 6 pulses А В С NAND output 0

Turns MOD 8 counter into a MOD 6 counter

## **Changing the MOD number:**

- 1. Find the smallest MOD required so that 2<sup>N</sup> is greater than or equal to the requirement.

- 2. Connect a NAND gate to the asynchronous CLEAR inputs of all flip flops.

- Determine which flip flops are HIGH <u>at the first</u> <u>undesired count</u> and connect the outputs of these flip flops to the NAND gate inputs.

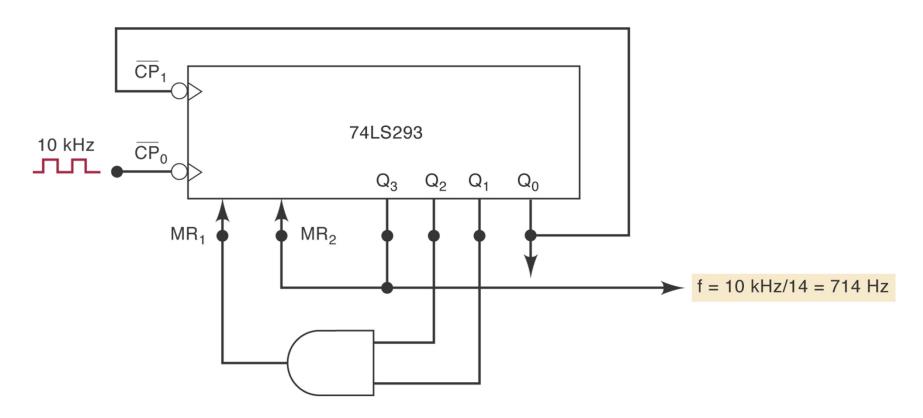

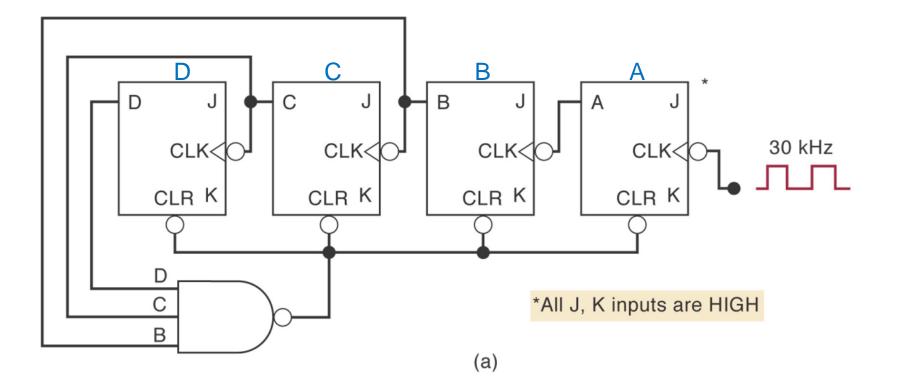

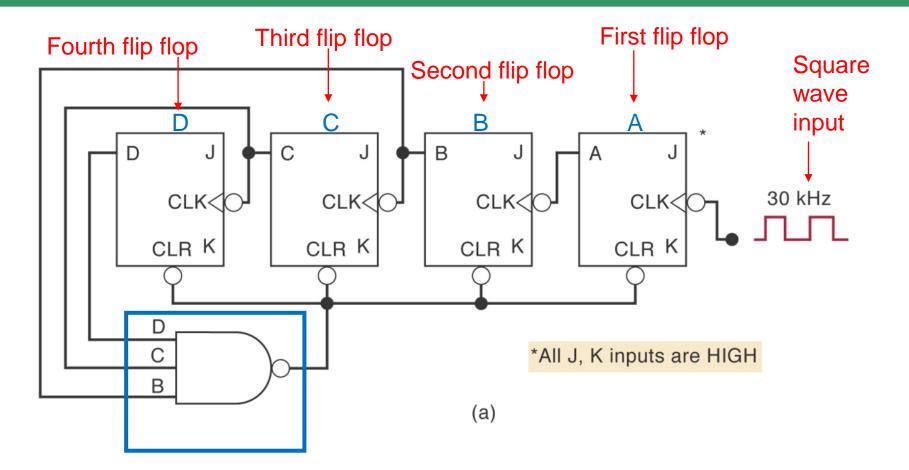

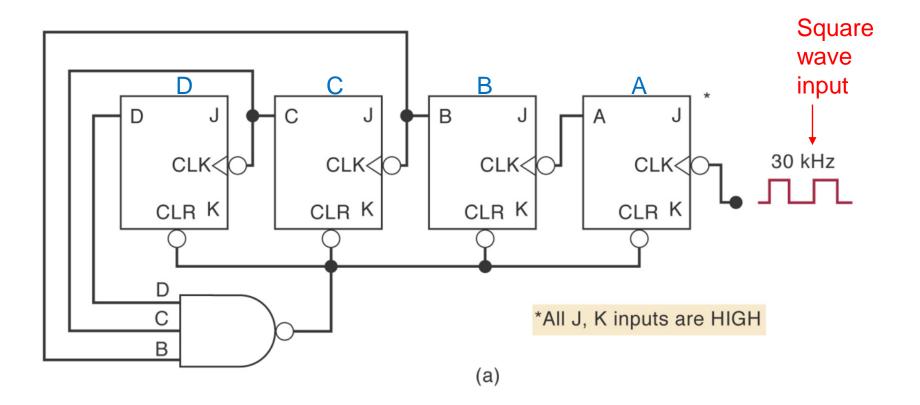

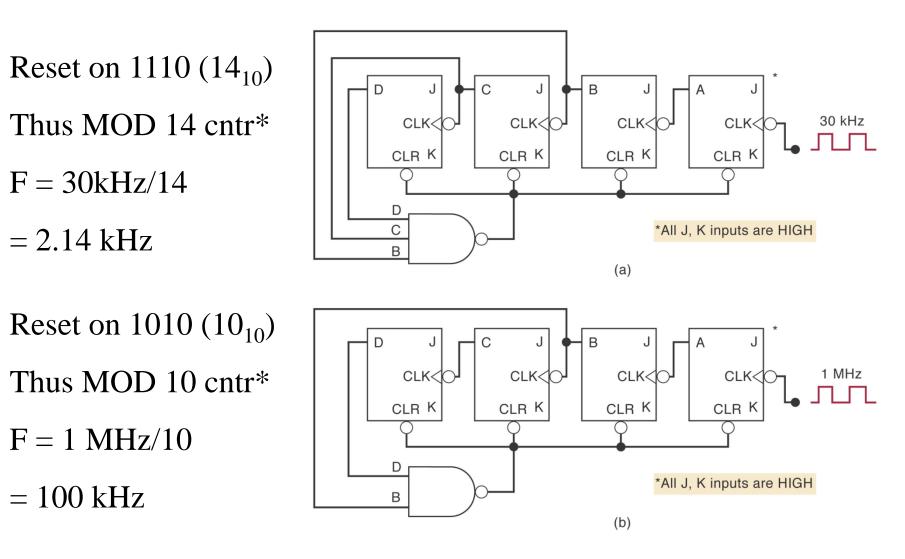

Reset on 1110 (14<sub>10</sub>) therefore it is a MOD 14 counter Frequency = 30kHz/14 = 2.14 kHz

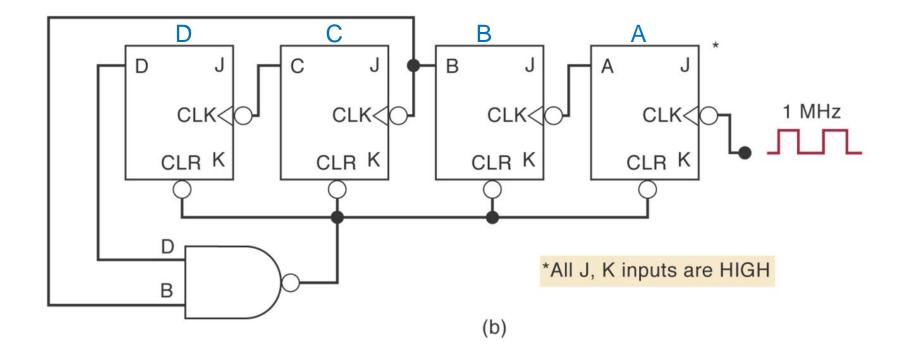

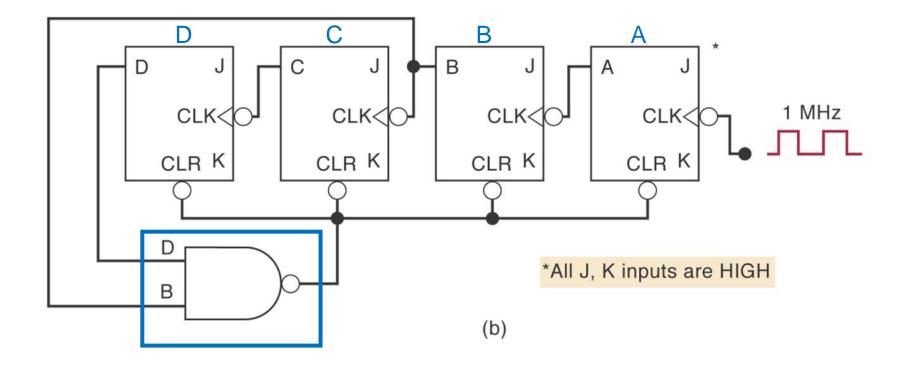

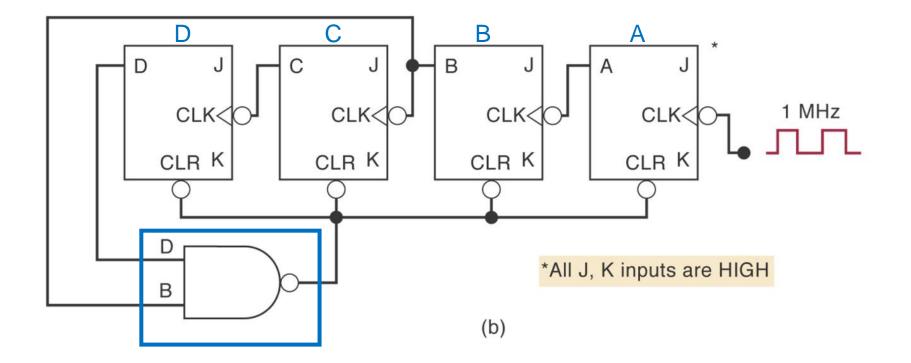

Reset on 1010  $(10_{10})$  therefore it is a MOD 10 counter Frequency = 1 MHz/10 = 100 kHz

\* The reset state is not a counting state

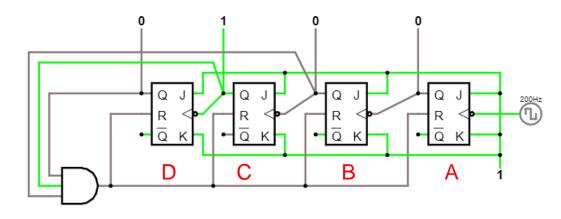

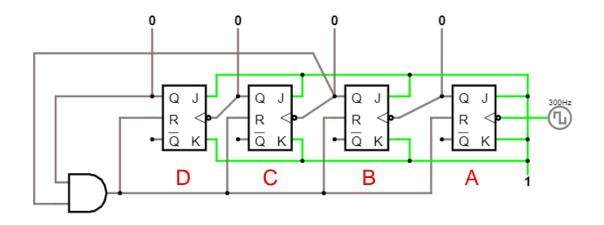

### Using the circuit simulator:

All J, K and inputs are HIGH

### Examples of counters with MOD Number $< 2^{N}$

- 1. Decade counters or BCD counters

- A decade counter is any counter with 10 distinct states, regardless of the sequence. Any MOD-10 counter is a decade counter.

- A BCD counter is a decade counter that counts from binary 0000 to 1001.

Decade counters are widely used for counting events and displaying results in decimal form.

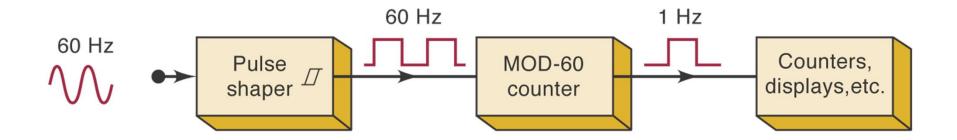

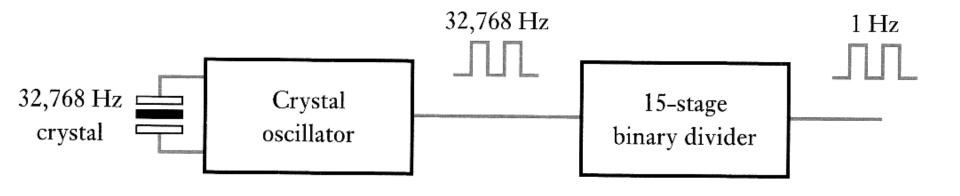

### 2. Designing a MOD 60 Counter

Your electronic watch will most likely contain a quartz crystal resonator oscillating at a frequency of 32 768 Hz ?

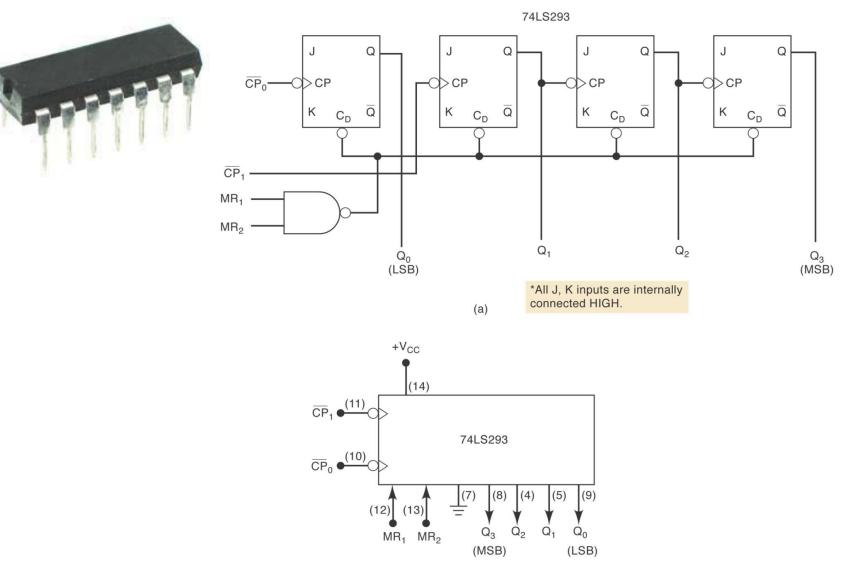

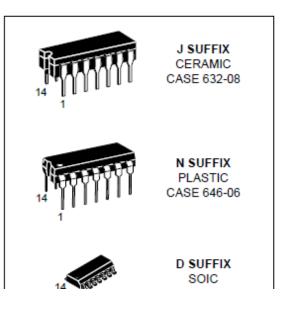

### An IC asynchronous counter – the 74LS293

### An IC asynchronous counter – the 74LS293

NOTOROLA

#### DECADE COUNTER; **4-BIT BINARY COUNTER**

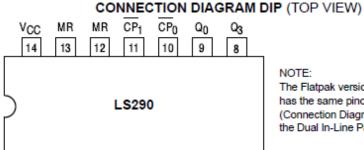

The SN54/74LS290 and SN54/74LS293 are high-speed 4-bit ripple type counters partitioned into two sections. Each counter has a divide-by-two section and either a divide-by-five (LS290) or divide-by-eight (LS293) section which are triggered by a HIGH-to-LOW transition on the clock inputs. Each section can be used separately or tied together (Q to CP)to form BCD, Bi-guinary, or Modulo-16 counters. Both of the counters have a 2-input gated Master Reset (Clear), and the LS290 also has a 2-input gated Master Set (Preset 9).

- Corner Power Pin Versions of the LS90 and LS93

- Low Power Consumption . . . Typically 45 mW

- High Count Rates . . . Typically 42 MHz

- Choice of Counting Modes . . . BCD, Bi-Quinary, Binary

- Input Clamp Diodes Limit High Speed Termination Effects

NOTE: The Flatpak version has the same pinouts (Connection Diagram) as the Dual In-Line Package.

#### SN54/74LS290 SN54/74LS293

#### DECADE COUNTER: 4-BIT BINARY COUNTER

LOW POWER SCHOTTKY

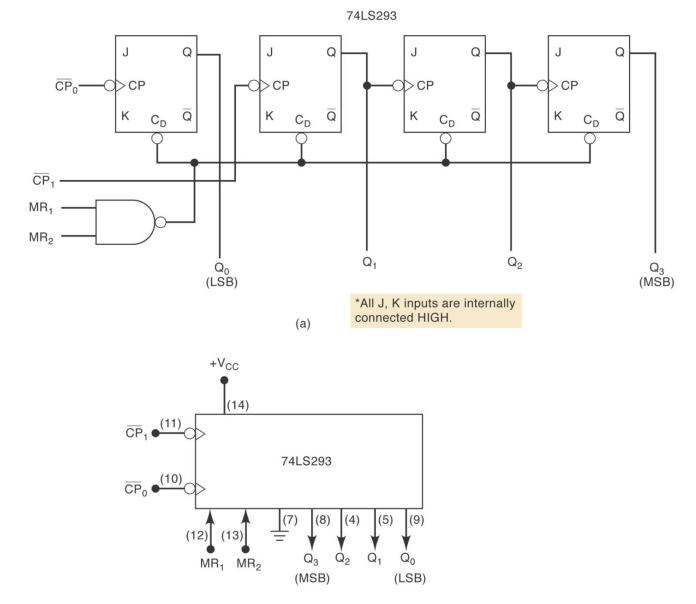

### An IC asynchronous counter – the 74LS293

- 4 JK flip flop (FFs)

- Each FF has NGT CP (CLK) input

– Each FF has active low asynchronous CLEAR inputs (MR<sub>1</sub> and MR<sub>2</sub> through NAND gate). Both MR I/P's must be HI to clear the counter to 0000.

- FF's  $Q_1$ ,  $Q_2$ , and  $Q_3$  are connected as a 3 bit ripple counter.  $Q_0$  is not connected internally, which allows flexibility in design.

#### 74LS293 as a MOD 16 counter

#### Should reset on 1010

#### Should reset on 1110