| ID Number  | : |

|------------|---|

| Full Name: |   |

# ECEN202 DIGITAL ELECTRONICS Practice TEST

2024

Time allowed: 60 MINUTES

#### **CLOSED BOOK**

**Permitted materials:** No programmable calculators are allowed.

No electronic dictionaries are allowed.

Paper foreign to English language dictionaries are

allowed.

**Instructions:** Attempt ALL questions.

There are 4 questions in this test paper:

# Space for working out your solutions is provided at the end of every section.

| Question | Topic                           | Allocated<br>Marks | Obtained<br>Marks |  |

|----------|---------------------------------|--------------------|-------------------|--|

| 1        | Logic and Boolean Algebra       | 25                 |                   |  |

| 2        | Combinational Logic             | 35                 |                   |  |

| 3        | Latches and Flip Flops          | 15                 |                   |  |

| 4        | Counters and Frequency Dividers | 25                 |                   |  |

|          | TOTAL                           | 100                |                   |  |

#### Question 1 - Logic and Boolean Algebra

25 marks

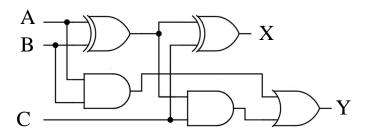

a) Write the Boolean expression for the outputs X and Y of the following circuit. (10 marks)

X = A xor B xor C = (A'B+AB') C'+(A'B+AB') C'

Y = AB + C (A xor B)

b) Draw a circuit diagram for **X** in part a) using only AND, OR and NOT gates. (8 marks)

c) Simplify using Boolean Algebra

(3 marks)

$$X = (\overline{AB})(\overline{A} + B)(\overline{B} + B)$$

$$= (\overline{A} + \overline{B})(\overline{A} + \overline{B})$$

$$= \overline{A} + \overline{A} + \overline{B} + \overline{B} + \overline{B}$$

$$= \overline{A} + \overline{A} + \overline{B} + \overline{B} + \overline{B}$$

a) Simplify using Boolean Algebra

(4 marks)

$$X = ABC + A\overline{B}(\overline{A}\overline{C})$$

$$= ABC + AB(\overline{A}C)$$

$$= ABC + AB(A+C)$$

$$= ABC + AB + ABC$$

$$= ACC + AB$$

$$= A(C+B)$$

#### **Question 2 – Combinational Logic**

35 marks

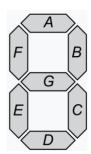

We want to design a logic circuit for a 7-segment LED display shown below.

The inputs are 4 binary digits **d**, **c**, **b**, **a**, which represent the number to be displayed on the LED. Bit **d** is the most significant bit (MSB), and **a** is the least significant bit (LSB). Each LED segment (labelled A, B, C, ... G on the diagram) has its own logic. For example, LED D is ON when **dcba** represent decimal numbers 0, 2, 3, 5, 6, 8 or 9.

a) Produce a truth table to drive LED labelled E 0 2 6 8

(10 marks)

| d | c | b | a | E |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 0 | 1 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | X |

| 1 | 0 | 1 | 1 | X |

| 1 | 1 | 0 | 0 | X |

| 1 | 1 | 0 | 1 | X |

| 1 | 1 | 1 | 0 | X |

| 1 | 1 | 1 | 1 | X |

b) Write the sum-of-products (SOP) expression for E

(5 marks)

E=d'c'b'a' + d'c'b a' +d'cba' +d c'b'a'

c) Use a K-map to simplify the logic expression for E.

(10 marks)

(Write your answer in the table provided below. Clearly mark the loop(s) of adjacent 1s.

|      | b'a' | b'a | ba | ba' |

|------|------|-----|----|-----|

| ďc'  | 1    | 0   | 0  | 1   |

| d'c  | 0    | 0   | 0  | 1   |

| dc   | X    | X   | X  | X   |

| dc'/ | 1    | 0   | X  | X   |

$$E = c'a' + ba' = a'(b+c')$$

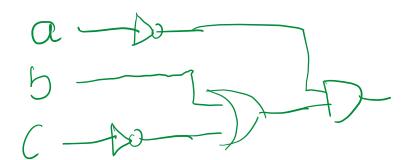

d) Draw a logic diagram for G using as few gates as possible.

(10 marks)

[CLEARLY write your ID number in the space shown above]

#### **Question 3 – Latches and Flip Flops**

15 marks

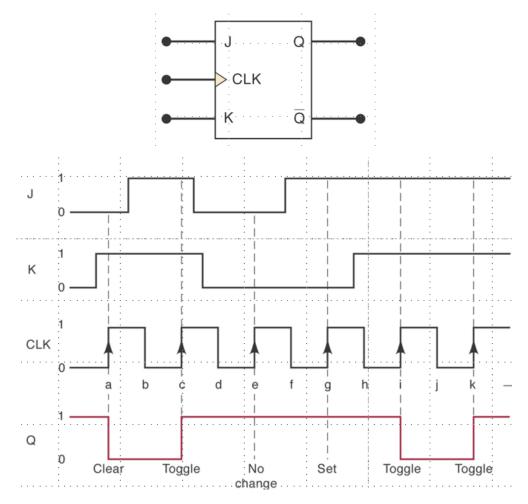

For the Flip Flop and the timing diagram below, draw the resulting output waveform Q. Explain the reason for each change in the value of Q. Assume Q starts high.

#### **Question 4 – Counters and Frequency Dividers**

25 marks

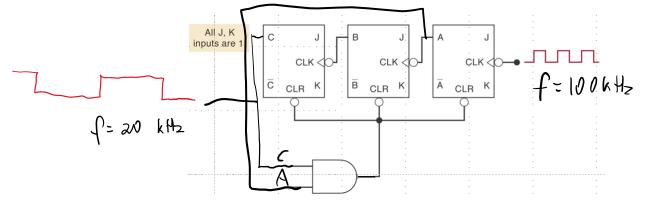

a) Using J-K Flip Flops, design a circuit that produces a 20 kHz clock from a 100kHz clock. You must use an **asynchronous** design. (7 marks)

To divide the clock by 5, we need a MOD 5 counter. Thus, we use 3 JK FFs and use C=A=1 to reset it at 5. All J,K inputs = 1.

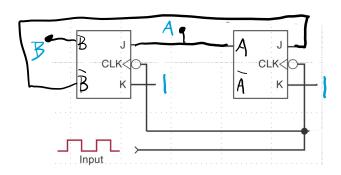

b) Using J-K Flip Flops, design a logic circuit that produces a 30 kHz clock from a 90 kHz clock. This time use a **synchronous** design. (18 marks) Hint: What is the Mod Number? How many FFs do you need? You can use the JK excitation table at the back of the test.

We require a MOD 3 counter, so 2 FFs are needed. The states of the counter are: 00 - 01 - 10 - 00 ... Use excitation table for JK:

| JU | Use ex                   | citatioi | i table i | Of JK |             |  |    |    |    |   |    |    |   |

|----|--------------------------|----------|-----------|-------|-------------|--|----|----|----|---|----|----|---|

|    | Q(                       | n)       |           | Q(n-  | <b>⊦1</b> ) |  | J1 |    | K1 | J | 0  | K0 |   |

|    | В                        | Α        |           | В     | Α           |  |    |    |    |   |    |    |   |

|    | 0                        | 0        |           | 0     | 1           |  | 0  |    | X  | 1 | L  | X  |   |

|    | 0                        | 1        |           | 1     | 0           |  | 1  |    | X  | ) | (  | 1  |   |

|    | 1                        | 0        |           | 0     | 0           |  | Х  |    | 1  | ( | )  | X  |   |

|    | 1                        | 1        |           | X     | X           |  | Х  |    | X  | > | (  | X  |   |

| J1 | Α'                       | Α        | <b>K1</b> | A'    | Α           |  | JO | A' | Α  |   | K0 | A' | Α |

| B' | 0                        | 1        | B'        | Х     | х           |  | B' | 1  | Х  |   | B' | Х  | 1 |

| В  | х                        | х        | В         | 1     | х           |  | В  | 0  | Х  |   | В  | Х  | х |

|    | J1=A, J0=B', K1=1, K0=1; |          |           |       |             |  |    |    |    |   |    |    |   |

|                                                         | ID Number: |

|---------------------------------------------------------|------------|

| [CLEARLY write your ID number in the space shown above] |            |

# **Fundamental Laws and Theorems of Boolean Algebra**

$$1. X + 0 = X$$

2.

$$X + 1 = 1$$

OR operations

3.

$$X + X = X$$

$$7. X.X = X$$

8.

$$X \cdot \overline{X} = 0$$

Double complement

10.

$$X + Y = Y + X$$

Commutative laws

12.

$$(X + Y) + Z = X + (Y + Z)$$

Associative laws

14.

$$X(Y + Z) = XY + XZ$$

Distribution Law

15.

$$X + Y . Z = (X + Y) . (X + Z)$$

Dual of Distributive Law

16.

$$X + XZ = X$$

Laws of absorption

$$17. \qquad X(X+Z) = X$$

18.

$$X+\overline{X}Y=X+Y$$

| Identity Theorems

19.

$$X(\overline{X}+Y)=X.Y$$

20.

$$\overline{X+Y} = \overline{X} \cdot \overline{Y}$$

De Morgan's Theorems

21.

$$\overline{X}.\overline{Y} = \overline{X} + \overline{Y}$$

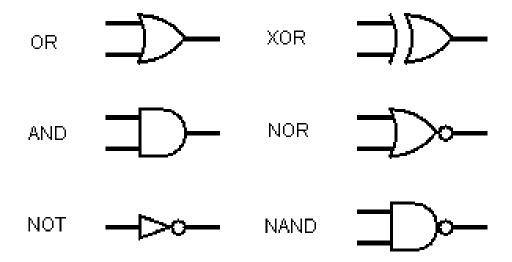

# **Logic Gate Symbols:**

### **Excitation tables:**

JK FF:

| Present | Next | J | K |

|---------|------|---|---|

| Q       | Q    |   |   |

| 0       | 0    | 0 | x |

| 0       | 1    | 1 | x |

| 1       | 0    | X | 1 |

| 1       | 1    | X | 0 |

## D FF:

| Present<br>State<br>Q(n) | Next State<br>Q(n+1) | Input<br>D |

|--------------------------|----------------------|------------|

| 0                        | 0                    | 0          |

| 0                        | 1                    | 1          |

| 1                        | 1                    | 1          |